# Oscad

# An open source EDA tool for circuit design, simulation, analysis and PCB design

Yogesh Save, Rakhi R, Shambhulingayya N. D. Rupak M. Rokade, Ambikeshwar Srivastava Manas Ranjan Das, Lavitha Pereira Sachin Patil, Srikant Patnaik Kannan M. Moudgalya

Indian Institute of Technology Bombay

Mr. Narendra Kumar Sinha, IAS An Electronics Engineer and a Bureaucrat, Who dreamt of educating all Indians through NMEICT and Who envisioned and made possible the Aakash Tablet

То

| Pı            | refac                     | е       |                                              | $\mathbf{i}\mathbf{x}$ |  |  |  |  |

|---------------|---------------------------|---------|----------------------------------------------|------------------------|--|--|--|--|

| A             | cknov                     | wledge  | ments                                        | xi                     |  |  |  |  |

| $\mathbf{Li}$ | $\operatorname{st}$ of    | Acrony  | yms                                          | xiii                   |  |  |  |  |

| 1             | Intr                      | oducti  | on                                           | 1                      |  |  |  |  |

| 2             | <b>Inst</b><br>2.1<br>2.2 | 0       |                                              |                        |  |  |  |  |

| 3             | Arc                       | hitectu | are of Oscad                                 | 13                     |  |  |  |  |

|               | 3.1                       | Modul   | les used in Oscad                            | 13                     |  |  |  |  |

|               |                           | 3.1.1   | EEschema                                     | 13                     |  |  |  |  |

|               |                           | 3.1.2   | CvPcb                                        | 14                     |  |  |  |  |

|               |                           | 3.1.3   | Pcbnew                                       | 14                     |  |  |  |  |

|               |                           | 3.1.4   | Model Builder                                | 15                     |  |  |  |  |

|               |                           | 3.1.5   | Subcircuit Builder                           | 16                     |  |  |  |  |

|               |                           | 3.1.6   | KiCad to Ngspice netlist converter           | 16                     |  |  |  |  |

|               |                           | 3.1.7   | Analysis Inserter                            | 16                     |  |  |  |  |

|               |                           | 3.1.8   | Ngspice                                      | 16                     |  |  |  |  |

|               |                           | 3.1.9   | Scilab based Mini Circuit Simulator (SMCSim) | 16                     |  |  |  |  |

|               | 3.2                       | Work    | flow of Oscad                                | 17                     |  |  |  |  |

| <b>4</b>      | Get                       | ting St | tarted                                       | 19                     |  |  |  |  |

|               | 4.1                       | Schem   | atic Editor                                  | 20                     |  |  |  |  |

|               | 4.2                       | Analys  | sis Inserter                                 | 20                     |  |  |  |  |

|               | 4.3                       | Netlist | Converter                                    | 22                     |  |  |  |  |

|               | 4.4                       | Ngspie  | ce                                           | 23                     |  |  |  |  |

|               | 4.5                       | Footpr  | rint Editor                                  | 24                     |  |  |  |  |

|   | 4.6            | Layout Editor |                                             |           |  |  |  |

|---|----------------|---------------|---------------------------------------------|-----------|--|--|--|

|   | 4.7            | SMCS          | im                                          | 25        |  |  |  |

|   | 4.8            | Model         | Builder                                     | 26        |  |  |  |

|   | 4.9            |               |                                             |           |  |  |  |

| 5 | $\mathbf{Sch}$ | ematic        | Creation                                    | 29        |  |  |  |

|   | 5.1            | Famili        | arising the Schematic Editor interface      | 29        |  |  |  |

|   |                | 5.1.1         | Top menu bar                                | 29        |  |  |  |

|   |                | 5.1.2         | Top toolbar                                 | 31        |  |  |  |

|   |                | 5.1.3         | Toolbar on the right                        | 32        |  |  |  |

|   |                | 5.1.4         | Toolbar on the left                         | 33        |  |  |  |

|   |                | 5.1.5         | Hotkeys                                     | 33        |  |  |  |

|   | 5.2            | Compo         | onents and component libraries              | 34        |  |  |  |

|   |                | 5.2.1         | Oscad libraries                             | 34        |  |  |  |

|   |                | 5.2.2         | Adding Oscad component libraries to project | 35        |  |  |  |

|   |                | 5.2.3         | Library browser                             | 35        |  |  |  |

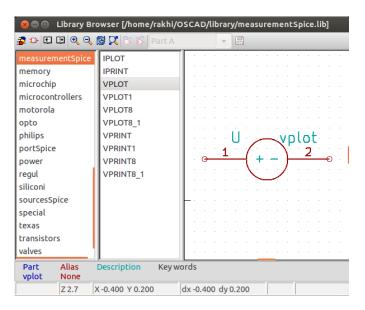

|   |                | 5.2.4         | Plot component library                      | 35        |  |  |  |

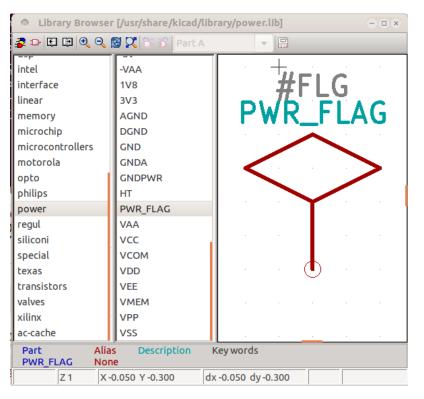

|   |                | 5.2.5         | Power component library                     | 35        |  |  |  |

|   |                | 5.2.6         | Connector library                           | 36        |  |  |  |

|   |                | 5.2.7         | Component references                        | 36        |  |  |  |

|   | 5.3            | Schem         | atic creation for simulation                | 37        |  |  |  |

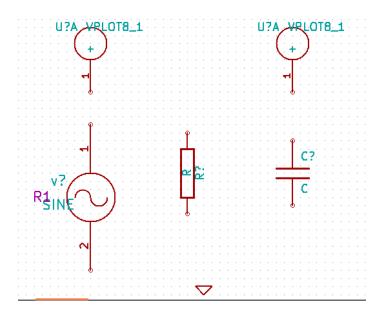

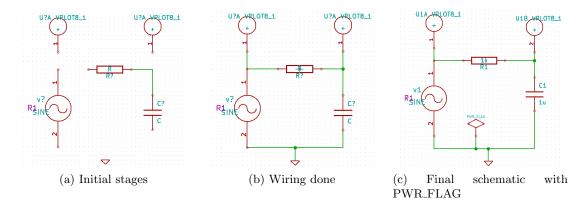

|   |                | 5.3.1         | Selection and placement of components       | 38        |  |  |  |

|   |                | 5.3.2         | Wiring the circuit                          | 39        |  |  |  |

|   |                | 5.3.3         | Assigning values to components              | 40        |  |  |  |

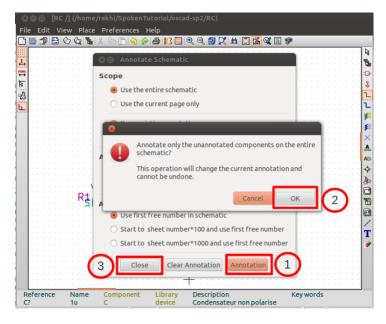

|   |                | 5.3.4         | Annotation and ERC                          | 40        |  |  |  |

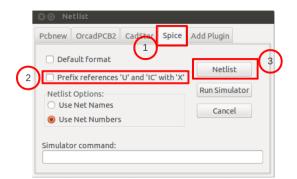

|   |                | 5.3.5         | Netlist generation                          | 43        |  |  |  |

| 6 | Sim            | ulatior       | 1                                           | <b>45</b> |  |  |  |

|   | 6.1            | Analys        | sis Inserter                                | 45        |  |  |  |

|   |                | 6.1.1         | Types of analysis                           | 46        |  |  |  |

|   |                | 6.1.2         | DC analysis inserter                        | 47        |  |  |  |

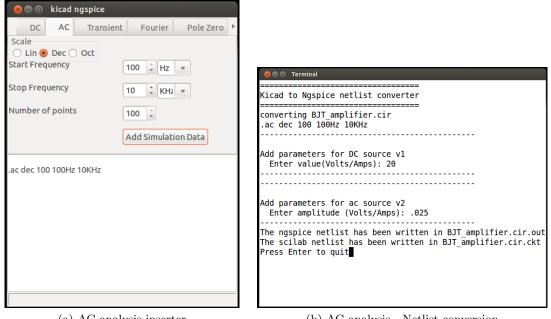

|   |                | 6.1.3         | AC analysis inserter                        | 48        |  |  |  |

|   |                | 6.1.4         | Transient analysis inserter                 | 49        |  |  |  |

|   |                | 6.1.5         | Saving the analysis file                    | 50        |  |  |  |

|   | 6.2            | Modify        | ying KiCad netlist for Ngspice simulation   | 50        |  |  |  |

|   | 6.3            |               | ples                                        | 54        |  |  |  |

|   |                | 6.3.1         | DC analysis                                 | 54        |  |  |  |

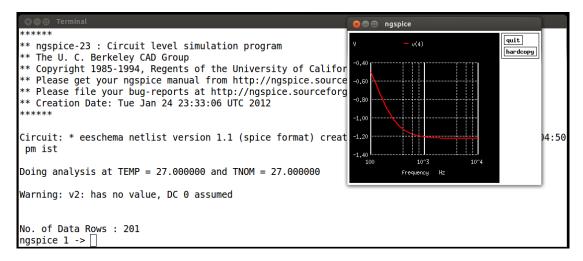

|   |                | 6.3.2         | AC small-signal analysis                    | 55        |  |  |  |

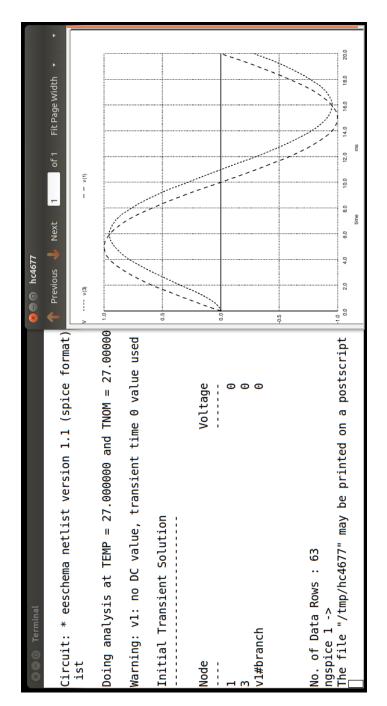

|   |                | 6.3.3         | Transient analysis                          | 57        |  |  |  |

| 7 PCB Design |      |         |                                                         |          |

|--------------|------|---------|---------------------------------------------------------|----------|

|              | 7.1  | Schem   | atic creation for PCB design                            | 61       |

|              |      | 7.1.1   | Netlist generation for PCB                              | 61       |

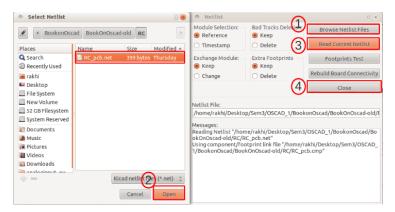

|              |      | 7.1.2   | Mapping of components using Footprint Editor            | 62       |

|              |      | 7.1.3   | Familiarising the Footprint Editor tool                 | 63       |

|              |      | 7.1.4   | Viewing footprints in 2D and 3D                         | 64       |

|              |      | 7.1.5   | Mapping of components in the RC circuit                 | 64       |

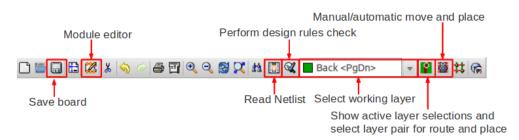

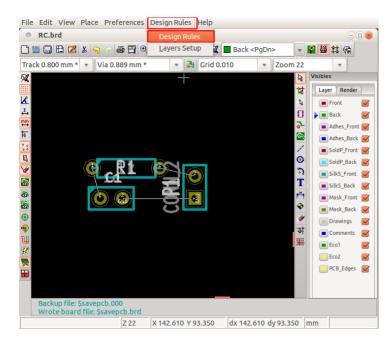

|              | 7.2  | Creatie | on of PCB layout                                        | 65       |

|              |      | 7.2.1   | Familiarising the Layout Editor tool                    | 66       |

|              |      | 7.2.2   | Hotkeys                                                 | 68       |

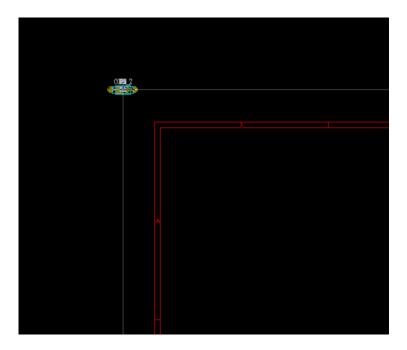

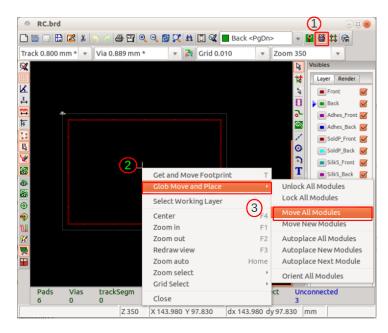

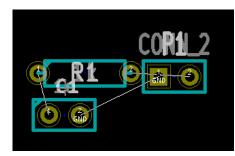

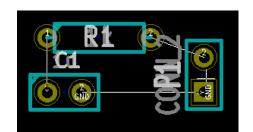

|              |      | 7.2.3   | PCB design example using RC circuit                     | 68       |

| 8            | Mod  | del Bu  | ilder and Subcircuit Builder                            | 77       |

|              | 8.1  | Model   | Builder                                                 | 77       |

|              |      | 8.1.1   | Example                                                 | 77       |

|              | 8.2  | Subcir  | cuit Builder                                            | 80       |

|              |      | 8.2.1   | Example                                                 | 80       |

| 9            | Scil | ab Bas  | ed Circuit Simulation                                   | 85       |

|              | 9.1  | Operat  | ting point (DC) analysis                                | 86       |

|              | 9.2  | Transi  | ent analysis                                            | 87       |

| 10           |      | nd Spa  | oken Tutorials                                          | 89       |

| 10           |      | -       | ner level tutorials                                     | 89<br>89 |

|              | 10.1 | 0       | Introduction to Oscad                                   | 89       |

|              |      |         | Schematic creation and simulation using Oscad           | 90       |

|              |      |         | Designing circuit schematic in KiCad                    | 90<br>90 |

|              |      |         | Designing printed circuit board using Oscad             | 90       |

|              |      |         | Electric rules checking and netlist generation in KiCad | 91       |

|              |      |         | Mapping components in KiCad                             | 91       |

|              |      |         | Designing PCB in KiCad                                  | 91       |

|              | 10.2 |         | ced level tutorials                                     | 92       |

|              | -    |         | ction sheet                                             | 93       |

|              | 10.0 |         | The procedure to practice                               | 93       |

|              |      |         | Please ensure that                                      | 93       |

|              |      |         | Basic module                                            | 93       |

|              |      |         | Schematic creation and simulation                       | 94       |

|              |      |         | Designing printed circuit board                         | 94       |

| 11           | Osc  | ad on   | Aakash                                                  | 95       |

vii

| Α  | Solv                 | ved Examples from [1]                                                         | 97  |  |  |  |  |

|----|----------------------|-------------------------------------------------------------------------------|-----|--|--|--|--|

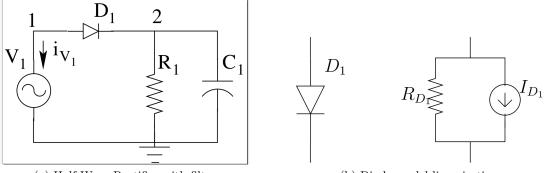

|    | A.1                  | Diode                                                                         | 97  |  |  |  |  |

|    |                      | A.1.1 Example 2.1 from [1]                                                    | 97  |  |  |  |  |

|    |                      | A.1.2 Example 2.5 from [1]                                                    | 101 |  |  |  |  |

|    | A.2                  | BJT: Example 3.1 from $[1]$                                                   | 104 |  |  |  |  |

|    | A.3                  | MOSFET: Example 4.5 from $[1]$                                                | 107 |  |  |  |  |

|    | A.4                  | OP-AMP                                                                        | 110 |  |  |  |  |

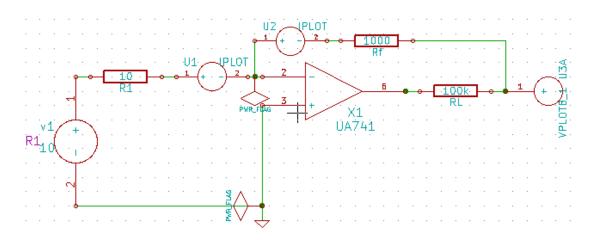

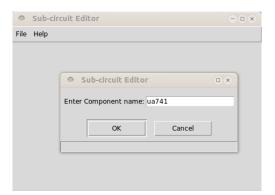

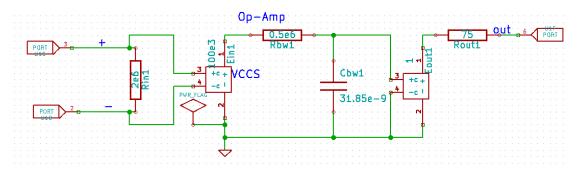

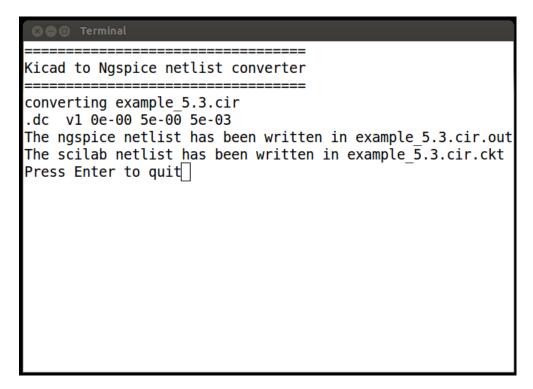

|    |                      | A.4.1 Example 5.3 from $[1]$                                                  | 110 |  |  |  |  |

|    |                      | A.4.2 Example 5.6 from [1]                                                    | 113 |  |  |  |  |

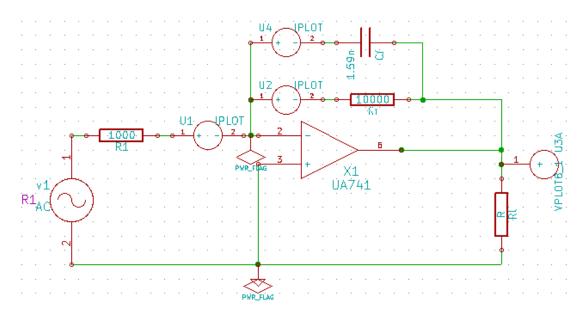

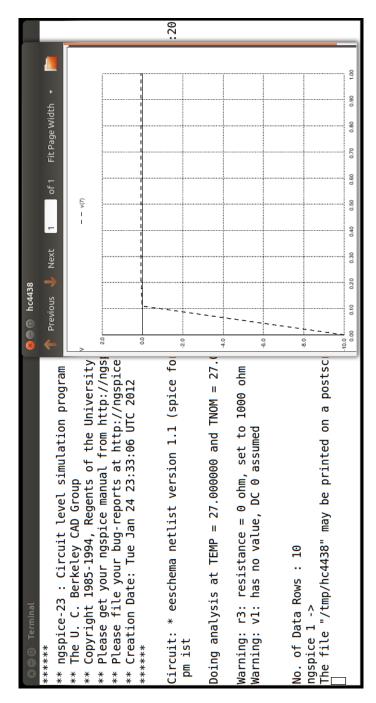

|    |                      | A.4.3 Example 5.7 from [1]                                                    | 116 |  |  |  |  |

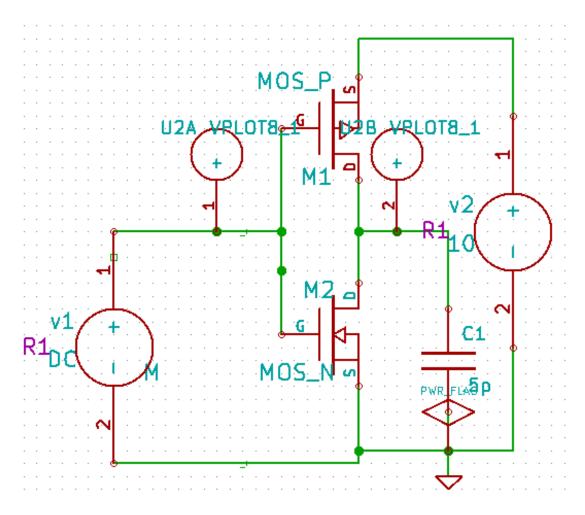

|    | A.5                  | CMOS Inverter: Example 9.4 from [1]                                           | 119 |  |  |  |  |

| в  | Osc                  | ad Resources                                                                  | 121 |  |  |  |  |

|    | B.1                  | SELF Workshops through Spoken Tutorials                                       | 121 |  |  |  |  |

|    | B.2                  | Textbook Companion on Oscad                                                   | 122 |  |  |  |  |

|    | B.3                  | Other Oscad Activities                                                        | 122 |  |  |  |  |

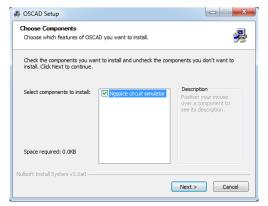

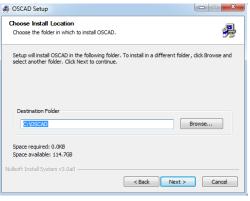

| С  | Osc                  | ad on Windows XP                                                              | 123 |  |  |  |  |

|    | C.1                  | Installing Oscad on Windows XP                                                | 123 |  |  |  |  |

|    | C.2                  | Procedure to set paths in the environment variable PATH for Windows           |     |  |  |  |  |

|    |                      | XP                                                                            | 124 |  |  |  |  |

|    | C.3                  | Special instructions to use Oscad on Windows XP $\ldots \ldots \ldots \ldots$ | 125 |  |  |  |  |

| Re | References           |                                                                               |     |  |  |  |  |

| In | $\operatorname{dex}$ |                                                                               | 131 |  |  |  |  |

| Aı | ıtho                 | r Information                                                                 | 133 |  |  |  |  |

viii

## Preface

Seeds for Oscad were sown when the National Mission on Education through ICT (NME-ICT) was launched: the mission document identified Adaption & deployment of open source simulation packages equivalent to Matlab, OrCAD, etc., as one of the areas NME-ICT would concentrate on. The FOSSEE (free and open source software in science and engineering education) group at IIT Bombay, of which we are a part of, initially started working on Python and Scilab. The Standing Committee of NMEICT encouraged us to contribute to other open source software as well. This push helped us develop Oscad, an open source alternative to OrCAD.

Oscad is an electronic design automation (EDA) tool, developed using KiCad, Ngspice and Scilab. We have made the netlist files generated by KiCad suitable for simulation through Ngspice. In order to provide an explanation facility, we have developed a method to automatically generate differential equations that describe a given analog circuit and to solve them using Scilab. Once satisfied with simulation results, the user can create a Gerber file for PCB fabrication.

While working on Scilab and Python, the FOSSEE group, jointly with the Spoken Tutorial team, created a large number of Spoken Tutorials [2]. Spoken Tutorials are audio-video tutorials in the IT and simulation areas, created for self learning using screencast technology. This instructional material has been used to train more than 20,000 college students on Scilab and Python in the past two years.

We have created seven spoken tutorials of ten minutes each, using which, a beginner level SELF workshop can be conducted on Oscad. We plan to conduct these workshops in about 100 colleges in the next one year, free of cost.

The FOSSEE team has also created more than 160 Scilab Textbook Companions, each of which contains Scilab code for worked out examples of standard textbooks, mostly in engineering and science. These have been created by the students and professors from various educational institutions in India. These textbooks can be downloaded free of cost from [3]. They can also be executed remotely on GARUDA cloud [4].

We are embarking on a similar methodology for Oscad as well: we have solved most of the worked out examples of [1] and given the solution in Appendix A. We hope to create Oscad Textbook Companions for all other relevant standard textbooks as well in the near future, once again through students and other volunteers. Solving the worked out examples of [1] was a good exercise, as it helped identify and include some missing features. The yet to be created Oscad Textbook Companions are expected to help in this regard, while simultaneously increasing the available documentation.

Lab migration is another important activity that the FOSSEE team is involved in. It provides equivalent Scilab code for Matlab based labs. This is also carried out through students and volunteers. We are starting this activity for Oscad as well: we will try to provide equivalent Oscad based solution to all circuit design labs that currently use proprietary software.

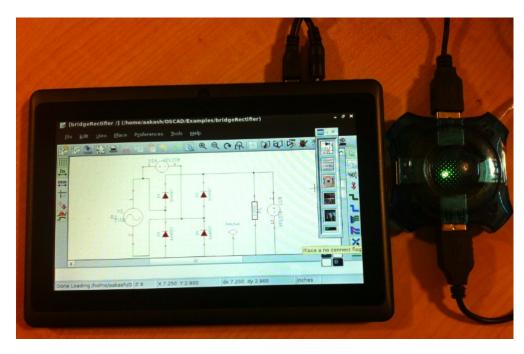

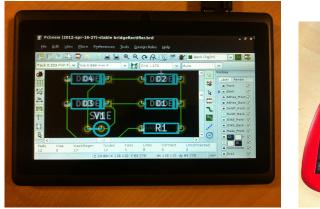

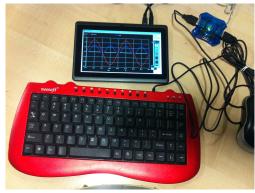

We have successfully ported Oscad on Aakash, the world's lowest cost computing tablet. As Ubuntu 12.10 runs on native mode on Aakash, we could port Oscad to it. Chapter 11 explains this activity, along with a few screenshots. As the Aakash tablet costs Rs. 2,263, and hence, for less than Rs. 2,500 (including a keyboard and a mouse), one can get access to a powerful EDA system. This is expected to help the students who are enthusiastic about circuit design, but cannot afford expensive hardware and software.

Porting of Oscad demonstrates the power of the concept of Aakash: an unlimited number of open source educational software systems can be made available even in a low cost device. Aakash can serve the dual purpose of a tablet and a computing device. This is the only way to address the aspirations of the millions of poor students who cannot afford even a computer system or an expensive tablet, let alone both.

The FOSSEE team is currently working on the promotion/development of the following open source software systems as well: 1. OpenFOAM, a CFD solver and an open source alternative to Fluent and StarCD. 2. COIN-OR, an open source software suite for optimisation problems. 3. OpenFormal for formal verification of computer software. About ten professors and 25 full time staff members and students are working on FOSSEE projects at IIT Bombay. Many more are expected to join in the near future.

Another important project supported by NMEICT is the Teach 10,000 Teachers (T10KT) programme. This methodology, pioneered at IIT Bombay [5,6] has demonstrated that it is possible for the best people in the field to provide extremely high quality training to a large number of learners simultaneously. Oscad is expected to be used in the forthcoming T10KT course on Analog Electronics, organised by IIT Kharagpur [7].

We invite all EDA enthusiasts to work with us through the following resources: 1. URL for all FOSSEE activities: http://fossee.in 2. URL for all Oscad resources: http://oscad.in 3. Textbook companion: textbook-companion@oscad.in 4. Lab migration: lab-migration@oscad.in 5. SELF workshops: SELF-workshop@oscad.in 6. Oscad development and enhancing its capabilities: Oscad-dev@oscad.in 7. Feedback on this book: Oscad-textbook@oscad.in. We also hope to establish forum based discussion services for Oscad.

Finally, an electronic version of this book is available for noncommercial purposes at http://oscad.in.

#### Acknowledgements

We would first like to thank Mr. N. K. Sinha, IAS, for without him, there would have been no National Mission on Education through ICT (NMEICT), without which, there would have been no FOSSEE, without which, there would have been no Oscad. The idealistic guiding principles of NMEICT, namely, reliance on open source software, providing free access to e-content, Internet connectivity for all educational institutions and providing a low cost access device to every student through Aakash, egged us to contribute our best and one of the outcomes is Oscad.

We would like to thank the former Human Resource Development Minister (HRM) Mr. Arjun Singh for getting NMEICT started. We would like to acknowledge the former HRM Mr. Kapil Sibal for his unstinting support and the faith he had in the NMEICT administration team. We would like to thank the current HRM Dr. Pallam Raju for extending the tenure of NMEICT by five more years.

We want to thank the Members of the Standing Committee of NMEICT who met once in two weeks for almost two years to review project proposals and to recommend them for funding or giving suggestions for improvement. We also want to thank them for urging us to work on more FOSS systems than what we were prepared for. Without this kind of active support, the ecosystem required for projects like Oscad to flourish, established at IIT Bombay through the many projects funded through NMEICT, would not have materialised.

We want to thank the FOSSEE faculty members Profs. Prabhu Ramachandran, Madhu Belur, Mani Bhushan, Shiva Gopalakrishnan, Jayendran Venkateswaran, Ashutosh Mahajan and Supratik Chakraborty for establishing a vibrant FOSSEE group at IIT Bombay. We want to thank Prof. D. B. Phatak for being a constant source of inspiration and encouragement and for supporting our activities directly and indirectly through the Teach 10,000 Teacher Programme [5] and the Aakash [8] Project. We want to thank other faculty members with NMEICT projects at IIT Bombay, namely, Profs. Kavi Arya, Ravi Poovaiah, Santosh Noronha, Anil Kulkarni, Sridhar Iyer, Sahana Murthy and Shishir Jha for sharing their dreams, processes and facilities. We want to thank the staff members of all NMEICT projects at IIT Bombay in general and of FOSSEE and Spoken Tutorial projects in particular, for providing a wonderful work environment.

We want to thank the IIT Bombay administration in general and R&D office in particular for providing us with an excellent environment to make us work efficiently. We want to thank the researchers and faculty members in our departments for providing us with necessary space and for putting up with our tantrums.

We would like to thank the professors, staff and students affiliated with the Wadhwani Electronics lab at IIT Bombay for trying out Oscad in lab courses and for the useful suggestions. We would like to thank Abhishek Pawar for creating Spoken Tutorials on KiCad. We would like to thank Saket Choudhary for making the netlist files generated by KiCad compatible with Ngspice. We want to thank Hardik for his help in implementing the current GUI of Oscad. We want to thank Kiran for designing the logo of Oscad. We want to thank Bella for helping with the coordination of FOSSEE in general and Oscad in particular. We want to thank Mr. Sunil Shastri of Shroff Publishers for bringing out this book in a short time.

Finally, we want to thank our family members for allowing us to work extended hours and for bearing with us.

Yogesh Save Rupak M. Rokade Lavitha Pereira Rakhi R Ambikeshwar Srivastava Sachin Patil Kannan M. Moudgalya

> IIT Bombay 22 May 2013

Shambhulingayya N. D. Manas Ranjan Das Srikant Patnaik

xii

## List of Acronyms

| ADC                  | Analog to Digital Converter                               |

|----------------------|-----------------------------------------------------------|

| BJT                  | Bipolar Junction Transistor                               |

| BV                   | Breakdown Voltage                                         |

| CCCS                 | Current Controlled Current Source                         |

| CCVS                 | Current Controlled Voltage Source                         |

| CPU                  | Central Processing Unit                                   |

| DAC                  | Digital to Analog Converter                               |

| DRC                  | Design Rules Check                                        |

| DXF                  | Drawing Interchange Format or Drawing Exchange Format     |

| EDA                  | Electronic Design Automation                              |

| ERC                  | Electric Rules Check                                      |

| FOSS                 | Free and Open Source Software                             |

| FPGA                 | Field Programmable Gate Array                             |

| gEDA                 | Electronic Design Automation released under GPL           |

| GUI                  | Graphical User Interface                                  |

| HDL                  | Hardware Descrition Language                              |

| HPGL                 | Hewlett-Packard Graphics Language                         |

| IC                   | Integrated Circuit                                        |

| ICT                  | Information and Communication Technology                  |

| IGBT                 | Insulated Gate Bipolar Transistor                         |

| JFET                 | Junction Field Effect Transistor                          |

| KCE                  | Kirchoff's Current Law                                    |

| KVE                  | Kirchoff's Voltage Law                                    |

| LXDE                 | Lightweight X11 Desktop Environment                       |

| MNA                  | Modified Nodal Analysis                                   |

| MOSFET               | Metal Oxide Semiconductor Field Effect Transistor         |

| NMEICT               | National Mission on Education through ICT                 |

| Op-amp               | Operational Amplifier                                     |

| OTC                  | Oscad Textbook Companion                                  |

| PCB                  | Printed Circuit Board                                     |

| RS                   | Ohmic Resistance                                          |

| SELF                 | Spoken Tutorial based Education and Learning through Free |

|                      | FOSS study                                                |

| SMCSim               | Scilab based Mini Circuit Simulator                       |

| $\operatorname{SVF}$ | Serial Vector Format                                      |

| T10KT                | Teach 10,000 Teachers                                     |

| VCCS                 | Voltage Controlled Current Source                         |

| VCVS                 | Voltage Controlled Voltage source                         |

|                      |                                                           |

List of Acronyms

$\operatorname{xiv}$

# Chapter 1 Introduction

Electronic systems are an integral part of human life. They have simplified our lives to a great extent. Starting from small systems made of a few discrete components to the present day integrated circuits (ICs) with millions of logic gates, electronic systems have undergone a sea change. As a result, design of electronic systems too have become extremely difficult and time consuming. Thanks to a host of computer aided design tools, we have been able to come up with quick and efficient designs. These are called Electronic Design Automation or EDA tools.

Let us see the steps involved in EDA. In the first stage, the specifications of the system are laid out. These specifications are then converted to a design. The design could be in the form of a circuit schematic, logical description using an HDL language, etc. The design is then simulated and re-designed, if needed, to achieve the desired results. Once simulation achieves the specifications, the design is either converted to a PCB, a chip layout, or ported to an FPGA. The final product is again tested for specifications. The whole cycle is repeated until desired results are obtained [9].

A person who builds an electronic system has to first design the circuit, produce a virtual representation of it through a schematic for easy comprehension, simulate it and finally convert it into a Printed Circuit Board (PCB). There are various tools available that help do this. Some of the popular EDA tools are those of Cadence, Synopys, Mentor Graphics and Xilinx. Although these are fairly comprehensive and high end, their licences are expensive, being proprietary.

There are some free and open source EDA tools like gEDA, KiCad and Ngspice. The main drawback of these open source tools is that they are not comprehensive. Some of them are capable of PCB design (e.g. KiCad) while some of them are capable of performing simulations (e.g. gEDA). To the best of our knowledge, there is no open source software that can perform circuit design, simulation and layout design together. Oscad is capable of doing all of the above.

Oscad is a free and open source EDA tool. It is an acronym for **O**pen source computer aided design. Oscad is created using open source software packages, such as

#### 1. Introduction

KiCad, Ngspice, Scilab and Python. Using Oscad, one can create circuit schematics, perform simulations and design PCB layouts. It can create or edit new device models, and create or edit subcircuits for simulation. It also has a Scilab based Mini Circuit Simulator (SMCSim), which is capable of giving the circuit equations for each simulation step. This feature is unique to Oscad. Because of these reasons, Oscad is expected to be useful to students, teachers and other professionals who would want to study and/or design electronic systems. Oscad is also useful for entrepreneurs and small scale enterprises who do not have the capability to invest in heavily priced proprietary tools.

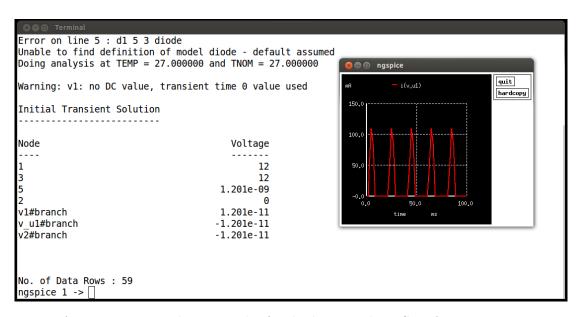

This book introduces Oscad to the reader and illustrates all the features of Oscad with examples. Chapter 2 gives step by step instructions to install Oscad on a typical computer system and to validate the installation. The software architecture of Oscad is presented in Chapter 3. Chapter 4 gets the user started with Oscad. It takes them through a tour of Oscad with the help of a simple RC circuit example. Chapter 5 explains how to create circuit schematics using Oscad, in detail using examples. Chapter 6 illustrates how to simulate circuits using Oscad. Chapter 7 explains PCB design using Oscad, in detail. The advanced features of Oscad such as Model Builder and Subcircuit Builder are covered in Chapter 8. Scilab based circuit simulator is covered in Chapter 9. Chapter 10 describes the spoken tutorials on Oscad and contains instructions to use them. Oscad is a light weight software and it has been ported to Aakash tablet. Chapter 11 explains about Oscad on Aakash. Appendix A presents examples, that have been worked out using Oscad, from the book Microelectronic Circuits by Sedra and Smith [1]. Appendix B explains the resources available for the use and promotion of Oscad.

The following convention has been adopted throughout this book. All the menu names, options under each menu item, tool names, certain points to be noted, etc., are given in *italics*. Some keywords, names of certain windows/dialog boxes, names of some files/projects/folders, messages displayed during an activity, names of websites, component references, etc., are given in typewriter font. Some key presses, e.g. Enter key, F1 key, y for yes, etc., are also mentioned in typewriter font.

## Chapter 2

## Installing and Setting up Oscad

The step by step instructions to install Oscad are given below. Installation script for Oscad is written in Bash. This makes the installation efficient and user friendly. Before starting the installation, one should ensure that all the system and installation requirements, and the prerequisites given below, are met. This chapter is presented in conversational style.

System requirements: The following are required.

- Ubuntu 12.04 OS (64-bit/32-bit)

- Scilab 5.4.0 or above (Optional)

Installation requirements: The following are required.

- working Internet connection

- admin (or root) privileges

- working knowledge and availability of Synaptic Package Manager [10]

**Prerequisites:** The following are required.

- Basic knowledge of analog and digital electronics

- Basic knowledge of Linux shell commands

Linux commands typed on terminal during installation are given in boxes with round corners

#### 2.1 Procedure for installing Oscad

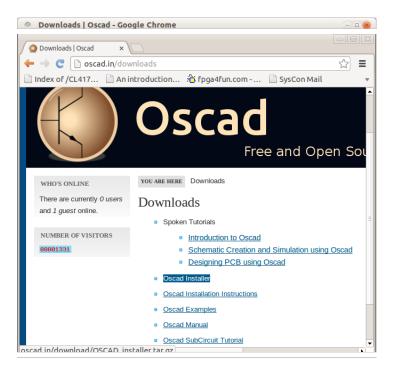

Step 1: Download Oscad and examples: Go to http://www.oscad.in/downloads. Fig. 2.1 shows the downloads page of Oscad website. Do the following:

- 1. Click on Oscad Installer and save the file, OSCAD\_installer.tar.gz.

- 2. Click on *Oscad Examples* and save the file, Examples.tar.gz, in the same folder as above.

Step 2: Download Scilab:

Note: Installation of Oscad can be done without Scilab

#### 2. Installing and Setting up Oscad

Figure 2.1: Oscad website

Scilab is used for simulating the circuit and giving symbolic equations If one does not need Scilab, skip this step and proceed to step 3 Go to http://www.scilab.org/. Click on the *Download Scilab* option on the

home page. Save the file in the same folder where OSCAD\_installer and Examples are saved. Fig. 2.2 shows the Download Scilab option on the Scilab web page. One can skip this step, if scilab 5.4.0 or above is already available in the system

- Step 3: Extract the downloaded files: Go to the folder where OSCAD\_installer, Examples and Scilab (Optional) files are saved. Select all, right click and choose *Extract Here* as shown in Fig. 2.3.

- Step 4: Navigate to folder: Go to the directory where all the three folders are saved and extracted. To do this, open a terminal window and type:

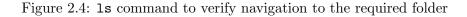

Cd folder-where-downloaded-files-are-saved. In this command, replace folder-where-downloaded-files-are-saved with the complete path of the folder where the downloaded files are saved and extracted. Press Enter. Now check whether you have navigated to desired folder by typing 1s and pressing Enter. Fig. 2.4 shows navigation to the folder having all files.

#### 2.1. Procedure for installing Oscad

Figure 2.2: Scilab website

| oscad-files                                             |             | -08                                                                                                                                                                                                                                             |

|---------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 🕐 👼 Home 🔎 Desktop Sem3 OSCAD_1                         | oscad-files | 🔶 🔶 🔍 Search                                                                                                                                                                                                                                    |

| tar.gz<br>Examples.tar.gz<br>OSCAD_installer.<br>tar.gz |             | Lbin.<br>Open With Archive Manager<br>Open With Archive Mounter<br>Cut<br>Copy<br>Make Links<br>Rename<br>Copy to<br>Move to<br>Move to<br>Move to<br>Trash<br>Send To<br>Revert to Previous Versions<br>Extract Here<br>Compress<br>Properties |

| 3 items selected (174.9 MB)                             |             |                                                                                                                                                                                                                                                 |

Figure 2.3: Extracting all files

**Step 5:** Navigate to OSCAD\_installer: To do this type cd OSCAD\_installer and press Enter. Fig. 2.5 shows that we have navigated to OSCAD\_installer folder.

2. Installing and Setting up Oscad

```

lavitha@fossee: ~/Downloads

lavitha@fossee: ~$ cd Downloads

lavitha@fossee: ~/Downloads$ ls

Examples OSCAD_installer scilab-5.4.1

lavitha@fossee: ~/Downloads$

```

Figure 2.5: Changing directory to OSCAD\_installer

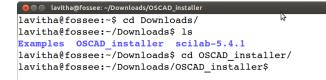

- Step 6: Make the installOSCAD and installModule files executable: To do this, type in the terminal sudo chmod 755 installOSCAD.sh installModule.sh and press Enter. Type the root password. The terminal should look like as shown in Fig. 2.6.

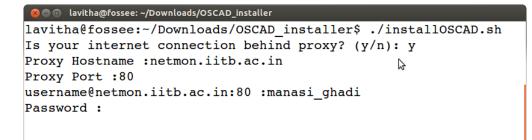

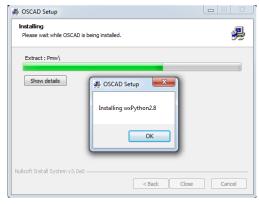

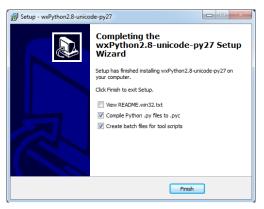

- Step 7: Begin installation: To begin the installation, type (./install0scad.sh) and press Enter. The terminal prompts for proxy settings as shown in Fig. 2.7.

Note: If one is not behind proxy, type  ${\tt n}$  and press  ${\tt Enter}.$

The option to enter proxy parameters will not be displayed.

If y is typed, then enter the proxy details as shown in Fig. 2.8. Now the prompt displays message Do you want to continue [y/n]:

Type y and press Enter. KiCad, Ngspice and necessary python modules will be installed automatically.

```

lavitha@fossee:-/Downloads/OSCAD_Installer

lavitha@fossee:-/Downloads/

lavitha@fossee:-/Downloads$ ls

Examples OSCAD_installer scilab-5.4.1

lavitha@fossee:-/Downloads$ cd OSCAD_installer/ b

lavitha@fossee:-/Downloads/OSCAD_installer$ sudo chmod 755 installOSCAD.sh install

Module.sh

[sudo] password for lavitha:

lavitha@fossee:-/Downloads/OSCAD_installer$

```

Figure 2.6: Making files executable using chmod command

6

2.1. Procedure for installing Oscad

```

@@@ lavitha@fossee:~/Downloads/OSCAD_installer

[sudo] password for lavitha:

lavitha@fossee:~/Downloads/OSCAD_installer$ ./installOSCAD.sh

Is your internet connection behind proxy? (y/n):

```

Figure 2.7: Terminal prompt for proxy settings during the installation of Oscad

Figure 2.8: Entering proxy details

```

Note: While installing python modules, one may get error messages

If so, install the missing packages using Synaptic Package Manager [10]

Once this is done, re-run the installOscad.sh script.

```

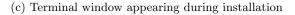

Step 8: Linking of Scilab: The prompt displays the message: Do you have scilab 5.4 or above? (y/n) as shown in Fig. 2.9. If one types n and presses the Enter key, it skips the linking of Scilab and goes to step 9. If instead, one types y and presses the Enter key, one has to type the complete path where Scilab (5.4.0 or

| 😣 🖻 💿 lavitha@fossee: ~/Downloads/OSCAD_installer |          |  |  |  |  |  |  |

|---------------------------------------------------|----------|--|--|--|--|--|--|

| Found python module: ImageTk                      |          |  |  |  |  |  |  |

| Found python module: string                       |          |  |  |  |  |  |  |

| Found python module: Tkinter                      |          |  |  |  |  |  |  |

| Found python module: Pmw                          |          |  |  |  |  |  |  |

| All python modules are available                  | <b>N</b> |  |  |  |  |  |  |

| Checking scilab                                   | \$       |  |  |  |  |  |  |

| Found scilab.                                     |          |  |  |  |  |  |  |

| Checking scilab version                           |          |  |  |  |  |  |  |

| Require scilab version 5.4 or above               |          |  |  |  |  |  |  |

| Do you have scilab5.4 or above? $(y/n)$           |          |  |  |  |  |  |  |

|                                                   |          |  |  |  |  |  |  |

Figure 2.9: Linking Scilab

| ⊗⊜ ◎ lavitha@fossee: ~/Downloads/OSCAD_installer                                                  |

|---------------------------------------------------------------------------------------------------|

| Use 'apt-get autoremove' to remove them.                                                          |

| 0 upgraded, 0 newly installed, 0 to remove and 30 not upgraded.                                   |

| Checking python Modules                                                                           |

| Found python module: wx                                                                           |

| Found python module: re                                                                           |

| Found python module: Image                                                                        |

| Found python module: ImageTk                                                                      |

| Found python module: string                                                                       |

| Found python module: Tkinter                                                                      |

| Found python module: Pmw                                                                          |

| All python modules are available                                                                  |

| Checking scilab                                                                                   |

| Found scilab.                                                                                     |

| Checking scilab version                                                                           |

| Require scilab version 5.4 or above                                                               |

| Do you have scilab5.4 or above? (y/n) y                                                           |

| Please give path of scilab installation directory (e.g., /home/lavitha/Downloads/scilab-5.4.0):/h |

| e/lavitha/Downloads/scilab-5.4.1                                                                  |

Figure 2.10: Giving directory information to link Scilab

above) has been saved. Example: (/home/lavitha/downloads/scilab-5.4.1.) Press Enter. Refer to Fig. 2.10. metanet library will be installed after this. It takes a couple of minutes.

Step 9: Final installation: The message Please select installation directory is displayed. Type the desired location where Oscad should be installed. For example: <a href="http://home/lavitha">/home/lavitha</a>. Press Enter. Once the installation is completed, the message Installation completed is displayed as shown in Fig. 2.11. This creates Oscad shortcut on Desktop.

#### 2.2 Testing

In order to check whether Oscad is correctly installed, we propose the following procedure:

- Double click on Oscad shortcut created on Desktop as shown in Fig. 2.12.

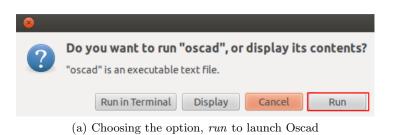

- A window is displayed as shown in Fig. 2.13a. Select the option *Run*. It opens the Oscad window as shown in Fig. 2.13b.

- Select *Project* tab at the top left hand corner of Oscad window and then click on *Open*. Browse to the folder where Examples are saved as shown in Fig. 2.14.

- Select RC from the examples by double clicking on RC and then click on OK.

- Enter Project name dialog box opens up as shown in Fig. 2.15. Click on OK.

- A toolbar appears as in Fig. 2.16a. Select *Schematic Editor* from the toolbar as shown in Fig. 2.16b.

- An error message as shown in Fig. 2.17a will pop up. Click on *Close*.

- Schematic Editor window appears. Press F1 to zoom in and press F2 to zoom out.

8

#### 2.2. Testing

```

😣 🗖 🗉 lavitha@fossee: ~/Downloads/OSCAD_installer

OSCAD/LPCSim/LUT/

OSCAD/OSCAD_installer/OSCAD_installer/

OSCAD/report/presentation/

OSCAD/Examples/

OSCAD/LPCSim/

OSCAD/OSCAD_installer/

OSCAD/report/

OSCAD/analysisInserter/

OSCAD/bin/

OSCAD/forntEnd/

OSCAD/images/

OSCAD/kicadtoNgspice/

OSCAD/library/

OSCAD/modelEditor/

OSCAD/modelLibrary/

OSCAD/subcktEditor/

OSCAD/subcktLibrary/

3

OSCAD/

/home/lavitha/OSCAD/setPathInstall.py

#!/usr/bin/python

OSCAD_HOME=set_PATH_to_OSCAD

/home/lavitha/OSCAD/setPath.py

#!/usr/bin/python

OSCAD_HOME=set_PATH_to_OSCAD

Installation completed

lavitha@fossee:~/Downloads/OSCAD_installer$

```

Figure 2.11: Terminal status when Oscad installation is completed

Figure 2.12: Oscad shortcut on the Desktop

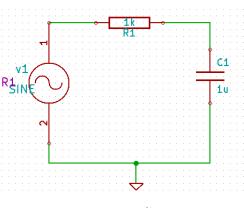

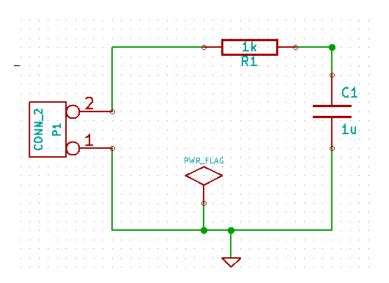

RC filter circuit seen on schematic editor window is as shown in Fig. 2.17b.

- Close Schematic Editor.

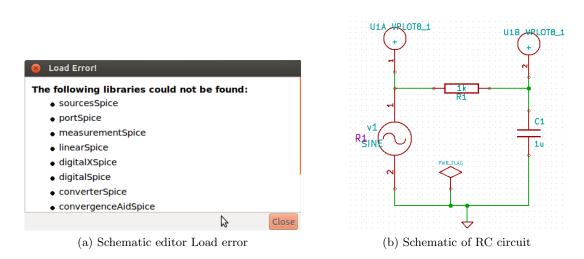

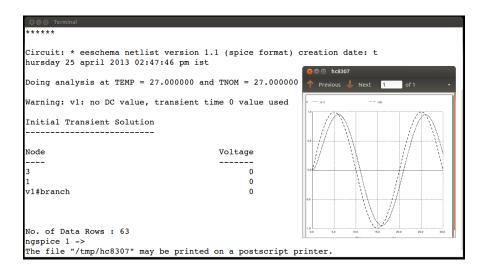

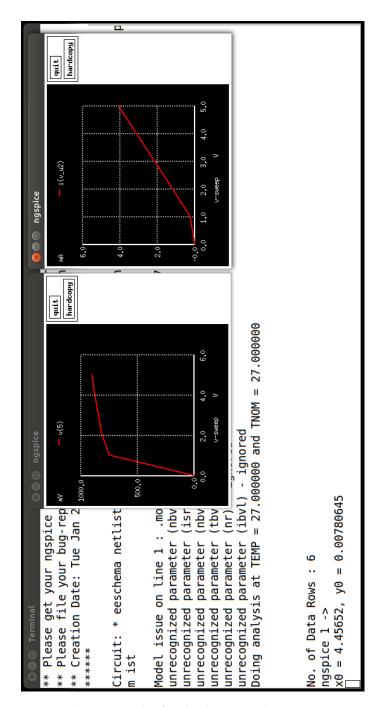

- Click on *Ngspice* from Oscad Toolbar as shown in Fig. 2.16c. This will simulate the netlist using Ngspice.

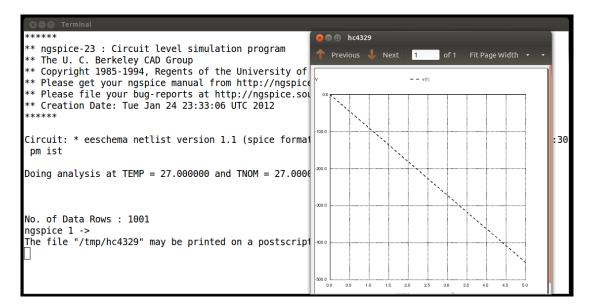

- The graph and terminal window appears as shown in Fig. 2.18. This shows the result of transient analysis of RC circuit and verifies installation.<sup>1</sup>

<sup>&</sup>lt;sup>1</sup>Note: Fig. 2.18 has Ngspice graph with white background. One would normally get Ngspice graphs with black background.

#### 2. Installing and Setting up Oscad

(b) Oscad window

Figure 2.13: Final stages in launching Oscad

| 😣 Choose Directory                                    |                                                  |   |                     |                |       |  |  |  |

|-------------------------------------------------------|--------------------------------------------------|---|---------------------|----------------|-------|--|--|--|

| Directory:                                            | /home/lavitha/Downloads/Example                  | s |                     |                | £     |  |  |  |

| s<br>:tifier<br>:tifierFilter<br>singJKFF<br>/Divider | <ul> <li>☐ linear1</li> <li>☐ linear2</li> </ul> |   | nonlı<br>RC<br>simp | nvert<br>leTTL | ingAm |  |  |  |

| •                                                     |                                                  |   |                     |                | Þ     |  |  |  |

| Selection:                                            | /home/lavitha/Downloads/Examples                 |   |                     | <u>0</u>       | к     |  |  |  |

|                                                       |                                                  |   |                     | <u>C</u> an    | cel   |  |  |  |

Figure 2.14: Browsing to the folder where Oscad examples are saved

| 😣 Oscad                |        |  |  |  |  |

|------------------------|--------|--|--|--|--|

| Enter Project name: RC |        |  |  |  |  |

| ОК                     | Cancel |  |  |  |  |

Figure 2.15: Dialog box to enter the project name

#### 2.2. Testing

(a) Default appearance

(c) Ngspice selected

Figure 2.16: Oscad toolbar

selected

Figure 2.17: Stages in opening the schematic of RC circuit

Figure 2.18: Transient analysis of RC circuit using Ngspice. Plots of v(3) and v(1) are shown, see Footnote 1 on Page 9.

### Chapter 3

## Architecture of Oscad

Oscad is a CAD tool that helps electronic system designers to design, test and analyse their circuits. But the important feature of this tool is that it is open source and hence the user can modify the source as per his/her need. The software provides a generic, modular and extensible platform for experiment with electronic circuits. This software runs on all Ubuntu Linux distributions. It uses Python, KiCad, Ngspice and Scilab (5.4.0 or above).

The objective behind the development of Oscad is to provide an open source EDA solution for electronics and electrical engineers. The software should be capable of performing schematic creation, PCB design and circuit simulation (analog, digital and mixed signal). It should provide facilities to create new models and components. In addition to this, it should have the capability to explain the circuit by giving symbolic equations and numerical values. The architecture of Oscad has been designed by keeping these objectives in mind.

#### 3.1 Modules used in Oscad

Various open-source tools have been used for the underlying build-up of Oscad. In this section we will give a brief idea about all the modules used in Oscad.

#### 3.1.1 EEschema

EEschema is an integrated software where all functions of circuit drawing, control, layout, library management and access to the PCB design software are carried out within itself. It is the schematic editor tool used in KiCad [11]. EEschema is intended to work with PCB layout software such as Pcbnew. It provides netlist that describes the electrical connections of the PCB. EEschema also integrates a component editor which allows the creation, editing and visualisation of components. It also allows the user to effectively handle the symbol libraries i.e; import, export, addition and deletion of library

#### 3. Architecture of Oscad

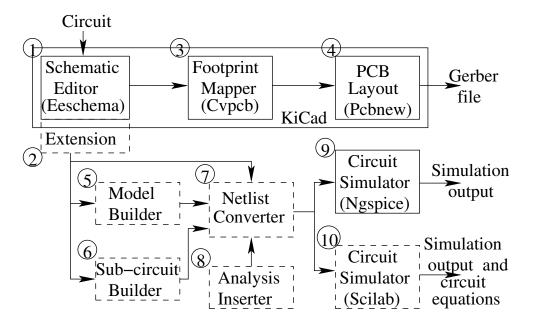

components. EEschema also integrates the following additional but essential functions needed for a modern schematic capture software: 1. Design rules check (DRC) for the automatic control of incorrect connections and inputs of components left unconnected. 2. Generation of layout files in POSTSCRIPT or HPGL format. 3. Generation of layout files printable via printer. 4. Bill of material generation. 5. Netlist generation for PCB layout or for simulation. This module is indicated by the label 1 in Fig. 3.1.

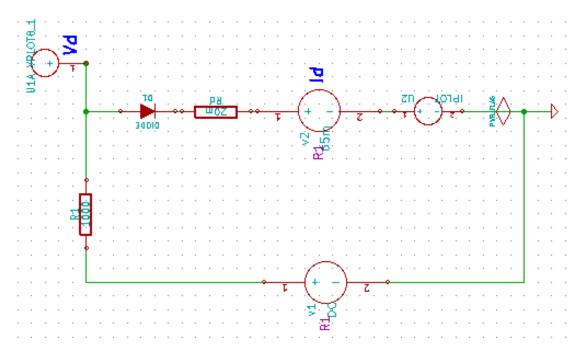

As Eeschema is originally intended for PCB Design, there are no fictitious components<sup>2</sup> such as voltage or current sources. Thus, we have added a new library for different types of voltage and current sources such as sine, pulse and square wave. We have also built a library which gives printing and plotting solutions. This extension, developed by us for Oscad, is indicated by the label 2 in Fig. 3.1.

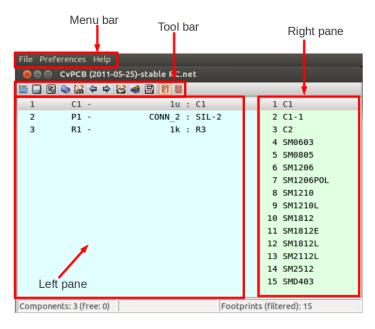

#### 3.1.2 CvPcb

CvPcb is a tool that allows the user to associate components in the schematic to component footprints when designing the printed circuit board. CvPcb is the footprint editor tool in KiCad [11]. Typically the netlist file generated by EEschema does not specify which printed circuit board footprint is associated with each component in the schematic. However, this is not always the case as component footprints can be associated during schematic capture by setting the component's footprint field. CvPcb provides a convenient method of associating footprints to components. It provides footprint list filtering, footprint viewing, and 3D component model viewing to help ensure that the correct footprint is associated with each component. Components can be assigned to their corresponding footprints manually or automatically by creating equivalence files. Equivalence files are look up tables associating each component with its footprint. This interactive approach is simpler and less error prone than directly associating footprints in the schematic editor. This is because CvPcb not only allows automatic association, but also allows to see the list of available footprints and displays them on the screen to ensure the correct footprint is being associated. This module is indicated by the label 3 in Fig. 3.1.

#### 3.1.3 Pcbnew

Pcbnew is a powerful printed circuit board software tool. It is the layout editor tool used in KiCad [11]. It is used in association with the schematic capture software EEschema, which provides the netlist. Netlist describes the electrical connections of the circuit. CvPcb is used to assign each component, in the netlist produced by EEschema, to a module that is used by Pcbnew. The features of Pcbnew are given below:

<sup>&</sup>lt;sup>2</sup>Signal generator or power supply is not a single component but in circuit simulation, we consider them as a component. While working with actual circuit, signal generator or power supply gives input to the circuit externally thus, doesn't require for PCB design.

#### 3.1. Modules used in Oscad

- It manages libraries of modules. Each module is a drawing of the physical component including its footprint the layout of pads providing connections to the component. The required modules are automatically loaded during the reading of the netlist produced by CvPcb.

- Pcbnew integrates automatically and immediately any circuit modification by removal of any erroneous tracks, addition of new components, or by modifying any value (and under certain conditions any reference) of the old or new modules, according to the electrical connections appearing in the schematic.

- This tool provides a rats nest display, a hairline connecting the pads of modules connected on the schematic. These connections move dynamically as track and module movements are made.

- It has an active Design Rules Check (DRC) which automatically indicates any error of track layout in real time.

- It automatically generates a copper plane, with or without thermal breaks on the pads.

- It has a simple but effective auto router to assist in the production of the circuit. An export/import in SPECCTRA dsn format allows to use more advanced autorouters.

- It provides options specifically for the production of ultra high frequency circuits (such as pads of trapezoidal and complex form, automatic layout of coils on the printed circuit).

- Pcbnew displays the elements (tracks, pads, texts, drawings and more) as actual size and according to personal preferences such as:

- display in full or outline.

- display the track/pad clearance.

This module is indicated by the label 4 in Fig. 3.1.

#### 3.1.4 Model Builder

This tool provides the facility to define a new model for devices such as, 1. Diode 2. Bipolar Junction Transistor (BJT) 3. Metal Oxide Semiconductor Field Effect Transistor (MOSFET) 4. Junction Field Effect Transistor (JFET) 5. IGBT and 6. Magnetic core. This module also helps edit existing models. It is developed by us for Oscad and it is indicated by the label 5 in Fig. 3.1. The use of this module is explained in detail in Sec. 8.1.

#### 3.1.5 Subcircuit Builder

This module allows the user to create a subcircuit for a component. Once the subcircuit for a component is created, the user can use it in other circuits. It has the facility to define new components such as, Op-amps and IC-555. This component also helps edit existing subcircuits. This module is developed by us for Oscad and it is indicated by the label 6 in Fig. 3.1. The use of this module is explained in detail in Sec. 8.2.

#### 3.1.6 KiCad to Ngspice netlist converter

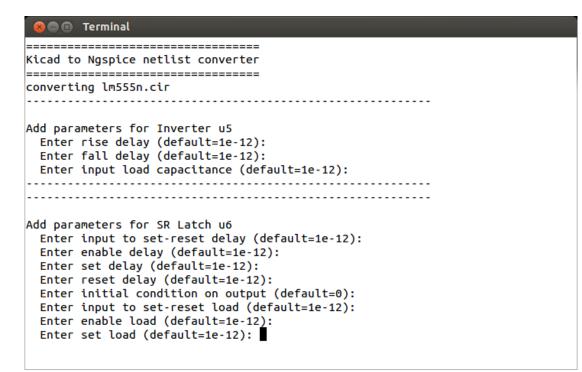

It converts KiCad generated netlists to Ngspice (see Sec. 3.1.8) compatible format. It has the capability to 1. Insert parameters for fictitious components 2. Convert IC into discrete blocks 3. Insert D-A and A-D converter at appropriate places 4. Insert plotting and printing statements in netlist and 5. Find current through all components.

This module is developed by us for Oscad and it is indicated by the label 7 in Fig. 3.1. The use of this module is explained in detail in Sec. 6.2.

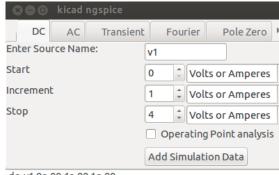

#### 3.1.7 Analysis Inserter

This feature helps the user to perform different types of analysis such as Operating point analysis, DC analysis, AC analysis and transient analysis. It has the facility to 1. insert type of analysis and 2. insert options for analysis. This module is developed by us for Oscad and it is indicated by the label 8 in Fig. 3.1. The use of this module is explained in Sec. 6.1.

#### 3.1.8 Ngspice

Ngspice is a general purpose circuit simulation program for nonlinear dc, nonlinear transient, and linear ac analyses [12]. Circuits may contain resistors, capacitors, inductors, mutual inductors, independent voltage and current sources, four types of dependent sources, lossless and lossy transmission lines (two separate implementations), switches, uniform distributed RC lines, and the five most common semiconductor devices: diodes, BJTs, JFETs, MESFETs, and MOSFET. This module is indicated by the label 9 in Fig. 3.1.

#### 3.1.9 Scilab based Mini Circuit Simulator (SMCSim)

We felt that an explanation capability would help students appreciate simulation results. This would also help students improve their circuits more easily. To this end, we have developed this module for Oscad, indicated by the label 10 in Fig. 3.1. SMCSim automatically generates the system of equations for the circuit under study and solves them using the state of the art open source simulator Scilab [3,13]. SMCSim works in three modes: normal, symbolic and numerical. SMCSim is explained in more detail in

Figure 3.1: Work flow in Oscad. Boxes with dotted lines denote the modules developed in this work.

Chapter 9. To the best of our knowledge, this facility is not available in any commercial simulator.

#### 3.2 Work flow of Oscad

Fig. 3.1 shows the work flow in Oscad. The block diagram consists of mainly three parts:

- Schematic Editor

- PCB Layout Editor

- Circuit Simulators

Here we explain the role of each block in designing electronic systems. Circuit design is the first step in the design of an electronic circuit. Generally a circuit diagram is drawn on a paper, and then entered into a computer using a schematic editor. EEschema is the schematic editor for Oscad. Thus all the functionalities of EEschema are naturally available in Oscad.

Libraries for components, explicitly or implicitly supported by Ngspice, have been created using the features of EEschema. As EEschema is originally intended for PCB design, there are no fictitious components such as voltage or current sources. Thus, a

#### 3. Architecture of Oscad

new library for different types of voltage and current sources such as sine, pulse and square wave, has been added in Oscad. A library which gives the functionality of printing and plotting has also been created.

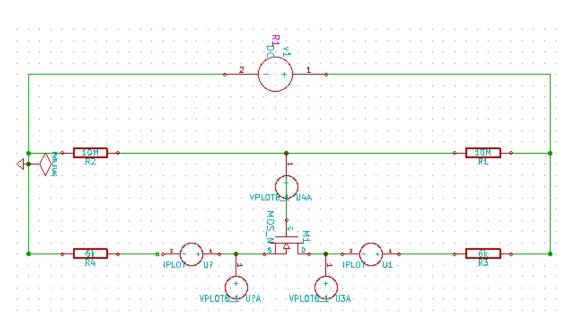

The schematic editor provides a netlist file, which describes the electrical connections of the design. In order to create a PCB layout, physical components are required to be mapped into their footprints. To perform component to footprint mapping, CvPcb is used. Footprints have been created for the components in the newly created libraries. Pcbnew is used to draw a PCB layout.

After designing a circuit, it is essential to check the integrity of the circuit design. In the case of large electronic circuits, breadboard testing is impractical. In such cases, electronic system designers rely heavily on simulation. The accuracy of the simulation results can be increased by accurate modeling of the circuit elements. Model Builder provides the facility to define a new model for devices and edit existing models. Complex circuit elements can be created by hierarchical modeling. Subcircuit Builder provides an easy way to create a subcircuit.

The netlist generated by Schematic Editor cannot be directly used for simulation due to compatibility issues. Netlist Converter converts it into Ngspice compatible format. The type of simulation to be performed and the corresponding options are provided through a graphical user interface (GUI). This is called Analysis Inserter in Oscad.

Oscad uses Ngspice for analog, digital, mixed-level/mixed-signal circuit simulation. Ngspice is based on three open source software packages [14]:

- Spice3f5 (analog circuit simulator)

- Cider1b1 (couples Spice3f5 circuit simulator to DSIM device simulator)

- Xspice (code modeling support and simulation of digital components through an event driven algorithm)

It is a part of gEDA project. Ngspice is capable of simulating devices with BSIM, EKV, HICUM, HiSim, PSP, and PTM models. It is widely used due to its accuracy even for the latest technology devices.

Oscad also has a Scilab based circuit simulator. It generates equations from the netlist and gets them solved by Scilab, which has many built in state of the art numerical methods. This tool is called Scilab based Mini Circuit Simulator (SMCSim) in Oscad.

### Chapter 4

## Getting Started

In this chapter we will get started with Oscad. We will run through the various options available with an example circuit. Referring to this chapter will make one familiar with Oscad and will help plan the project before actually designing a circuit. Lets get started.

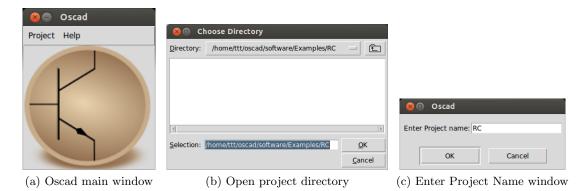

After one finishes installing Oscad, a shortcut link for Oscad will be created on the desktop. Double click on this link to launch Oscad. Oscad main window will open up. It is shown in Fig. 4.1a. On the menu bar there are two menus, *Project* and *Help*. To create a new project or open an existing project, use the *Project* menu.

Let us create a new project. Click on *Project* and select *New*. The Choose Directory window opens up. This window is shown in Fig. 4.1b. Browse to the desired directory. Click on OK. A new window opens up with Enter Project name field. Type the name of the new project here. Click on OK. A folder will be created in the specified directory. The name of this folder will be the same as that of the project created.

A vertical toolbar will appear. This toolbar is shown in Fig. 2.16a on Page 11. This is the Oscad toolbar.

Figure 4.1: Getting started with Oscad

Now let us see how to open an existing project. Click on *Project* and select *Open*. The Choose Directory window, as shown in Fig. 4.1b, opens up. Browse to the directory of the project. Choose RC from the Examples folder that has been downloaded from the Oscad web page (www.oscad.in). Click on OK. The Enter Project name window opens up. This window is illustrated in Fig. 4.1c. Since we are opening an already existing project, the project name will appear in the text box automatically. Click on OK.

The Oscad toolbar appears. It contains 9 tools. The tool icons have images depicting their purpose. If one places the mouse pointer on these tools, the name of the tool appears at the bottom of the mouse pointer. Following is the list of tools, from top to bottom as they appear, in the Oscad toolbar.

1. Schematic Editor 2. Analysis Inserter 3. Netlist Converter 4. Ngspice 5. Footprint Editor 6. Layout Editor 7. SMCSim 8. Model Builder 9. Subcircuit Builder.

#### 4.1 Schematic Editor

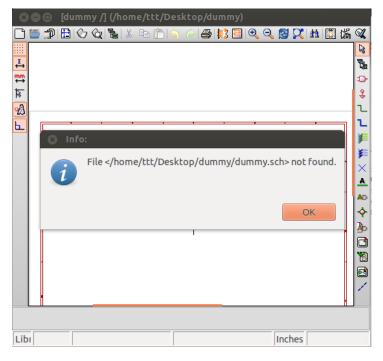

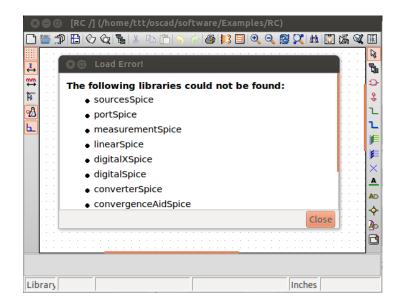

Click on the first tool on the toolbar i.e. *Schematic Editor*. Doing so will open EEschema, the schematic editor used in Oscad. If a new project is being created, one will get the schematic editor window with an info dialog box. This is illustrated in Fig. 4.2. This warning can be safely ignored by clicking on OK.

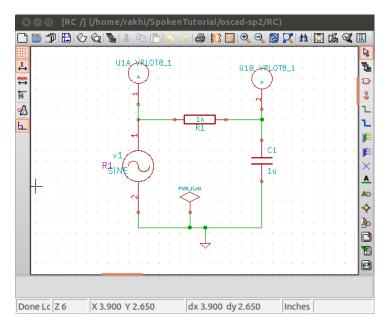

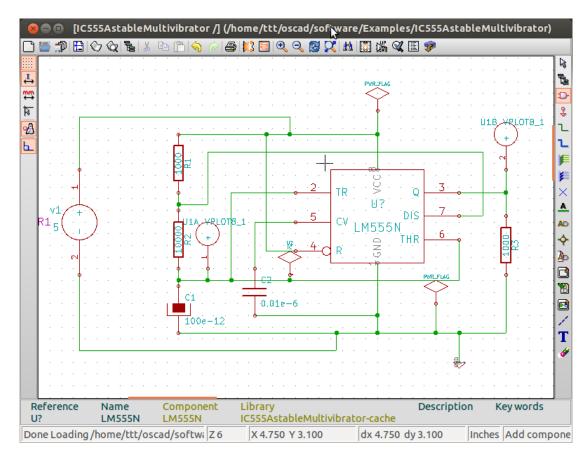

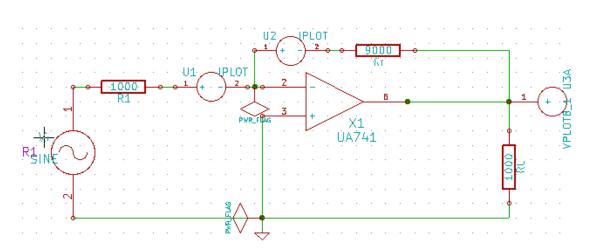

However, if an already existing project is opened, one would get the schematic editor window along with a Load error. This is illustrated in Fig. 4.3. This error occurs because the schematic that is opened has not been loaded with the libraries mentioned in the Load Error message. Sec. 5.2.2 explains how to load these libraries to the project. Close the Load Error message by clicking on the Close button. The RC circuit diagram opens up as shown in Fig. 4.4. Now the circuit schematic can be created/edited. To know how to use the schematic editor to create circuit schematics, refer to Chapter 5.

#### 4.2 Analysis Inserter

The second tool on the toolbar is the *Analysis Inserter*. Note that the spice netlist file (.cir) should be generated before using this tool. This is because this tool is used to insert analysis commands to the spice netlist file. To know how to generate the spice netlist file, refer to Sec. 5.3.5.

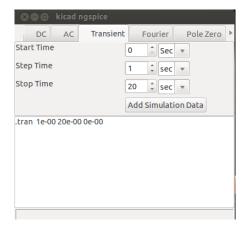

When one clicks on this tool, a window titled KiCad Ngspice will open. This is the Analysis Inserter GUI. It is shown in Fig. 4.5. This window helps the user to insert the analysis commands into the spice netlist file. The use of analysis inserter is explained in detail in Sec. 6.1.

#### 4.2. Analysis Inserter

Figure 4.2: Schematic Editor (opening a new project)

Figure 4.3: Schematic Editor (opening an already existing project)

Figure 4.4: Schematic Editor (with RC circuit)

| 80                 | 90   | kicad ngsp | ice     |                          |                     |                    | J |  |

|--------------------|------|------------|---------|--------------------------|---------------------|--------------------|---|--|

| ٦C                 | AC   | Transient  | Fourier | Pole Ze                  | го                  | Transfer Function  |   |  |

| Enter Source Name: |      |            |         |                          |                     |                    |   |  |

| Start              |      |            |         |                          | 0                   | Volts or Amperes 🔻 |   |  |

| Incre              | ment |            |         |                          | 0                   | Volts or Amperes 🔻 |   |  |

| Stop               |      |            |         |                          | 0                   | Volts or Amperes 🔻 |   |  |

|                    |      |            |         | Operating Point analysis |                     |                    |   |  |

|                    |      |            |         |                          | Add Simulation Data |                    |   |  |

|                    |      |            |         |                          |                     |                    |   |  |

|                    |      |            |         |                          |                     |                    |   |  |

|                    |      |            |         |                          |                     |                    |   |  |

|                    |      |            |         |                          |                     |                    |   |  |

|                    |      |            |         |                          |                     |                    |   |  |

|                    |      |            |         |                          |                     |                    |   |  |

|                    |      |            |         |                          |                     |                    |   |  |

|                    |      |            |         |                          |                     |                    |   |  |

Figure 4.5: Analysis Inserter

#### 4.3 Netlist Converter

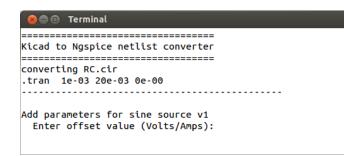

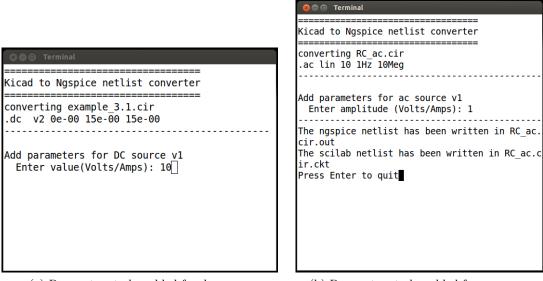

The third tool on the toolbar is the *Netlist Converter*. Before one uses this tool, one should have already created the spice netlist file and used analysis inserter to generate analysis commands. To know how to generate spice netlist, refer to Sec. 5.3.5. To know how to insert analysis commands to the netlist, refer to Chapter 6. This file is not directly usable for simulation. In other words, it is not compatible with Ngspice.

The spice netlist file contains only the component placement information and it

#### 4.4. Ngspice

Figure 4.6: Netlist Converter

Figure 4.7: Ngspice simulation result showing v(3) and v(1), see Footnote 1 on Page 9.

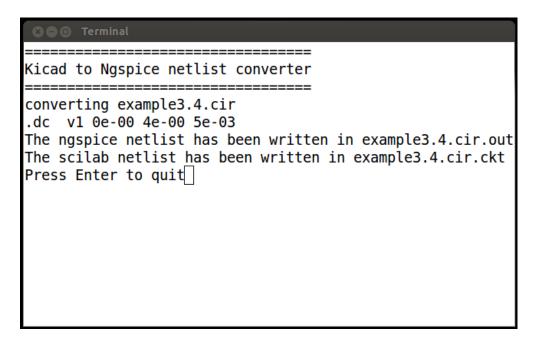

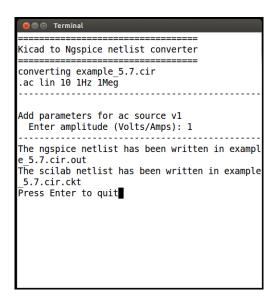

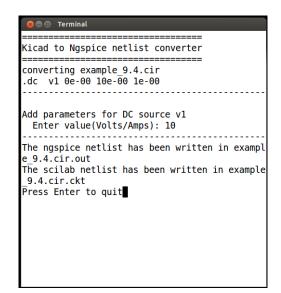

says nothing about the magnitude and other parameters (if applicable) of the source components like voltage source and current source. When one clicks on the *Netlist Converter* tool, a terminal window will open up as shown in Fig. 4.6. The terminal window displays the name of the .cir file it is referring to. It also asks for the source value. It may ask for other parameters depending upon the type of sources used. Once the values have been entered, press the Enter key. It will generate .cir.out and .cir.ckt files in the same project directory.

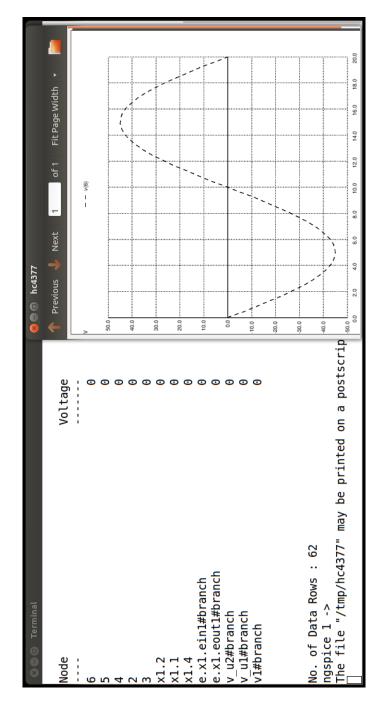

# 4.4 Ngspice

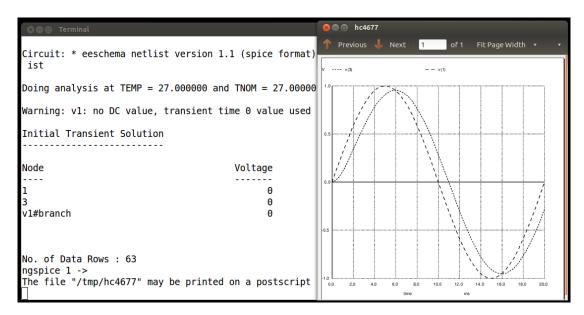

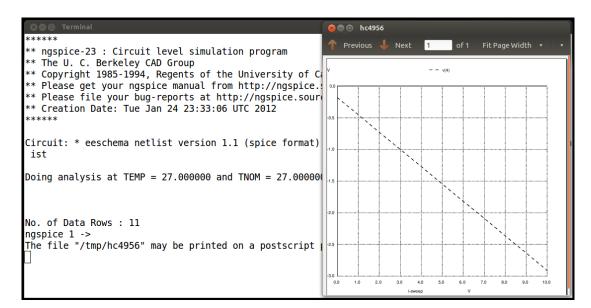

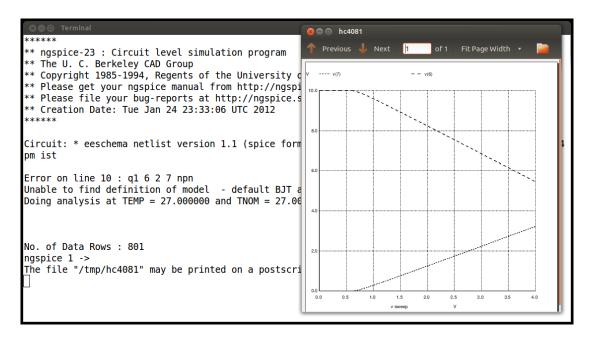

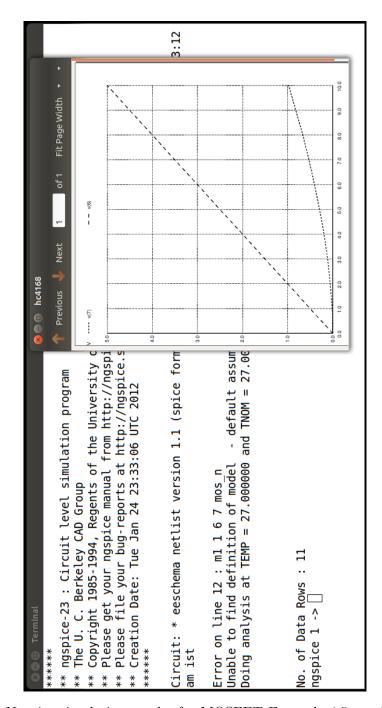

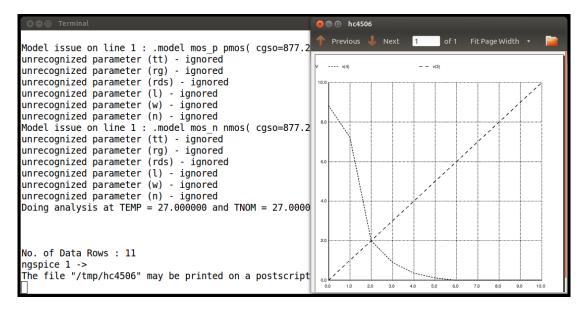

Sections 4.2 and 4.3 help generate a netlist suitable to be simulated using Ngspice. Clicking on the tool *Ngspice* will open a terminal window and a graph window as shown in Fig. 4.7. One should have the converted netlist file .cir.out before using this tool.

| 800     | CvPCB (2011-05    | i-25)-stable RC.net |                   |

|---------|-------------------|---------------------|-------------------|

| 들 🗔 I B | 5 🐟 🔛 🗢 😫         | 3 📣 🔜 🚺 🛢           |                   |

| 1       | C1 -              | 1u : C1             | 1 C1              |

| 2       | P1 -              | CONN_2 : SIL-2      | 2 C1-1            |

| 3       | R1 -              | 1k : R3             | 3 C2              |

|         |                   |                     | 4 SM0603          |

|         |                   |                     | 5 SM0805          |

|         |                   |                     | 6 SM1206          |

|         |                   |                     | 7 SM1206POL       |

|         |                   |                     | 8 SM1210          |

|         |                   |                     | 9 SM1210L         |

|         |                   |                     | 10 SM1812         |

|         |                   |                     | 11 SM1812E        |

| Compon  | ents: 3 (free: 0) | Footprin            | ts (filtered): 15 |

Figure 4.8: CvPcb window

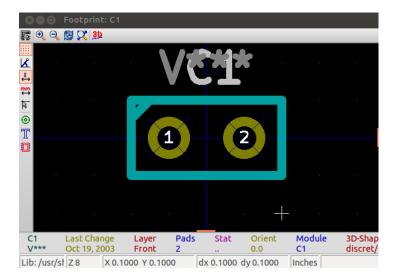

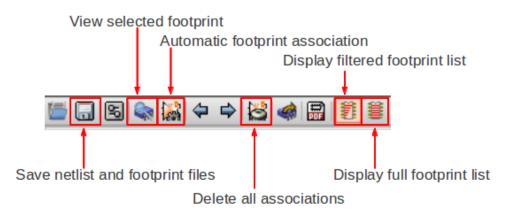

## 4.5 Footprint Editor

Clicking on the *Footprint Editor* tool will open the CvPcb window. This window will ideally open the .net file for the current project. So, before using this tool, one should have the netlist for PCB design (a .net file). To know more about how to generate netlist for PCB, refer to Sec. 7.1.1.

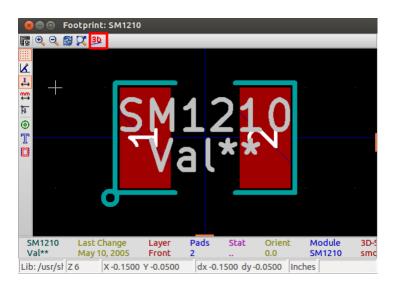

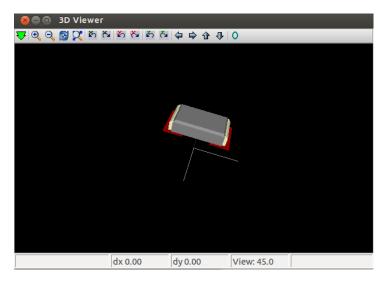

Open the project RC\_pcb available in the Examples folder downloaded from the Oscad website. On clicking the *Footprint Editor* tool, we see the corresponding RC\_pcb.net file for RC circuit. This window is shown in Fig. 4.8. The main purpose of this window is to let one choose the footprints for the various components in the circuit. Let us view the footprint C1 for capacitor C1. Click on C1 from the right hand side of CvPcb window. Click on *View Selected Footprint* tool from the tool bar of CvPcb window. This will show the footprint corresponding to C1. This is illustrated in Fig. 4.9. To know more about how to assign footprints to components, see Chapter 7.

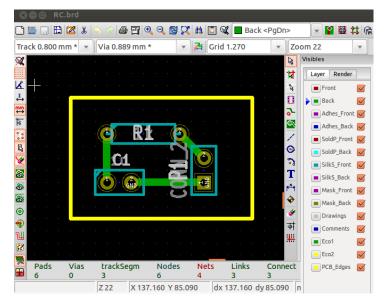

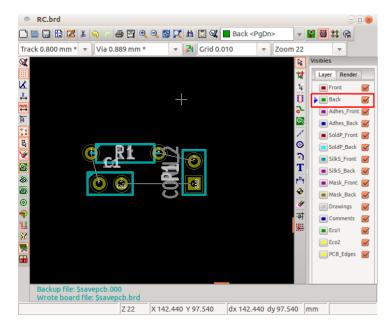

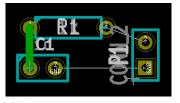

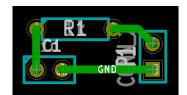

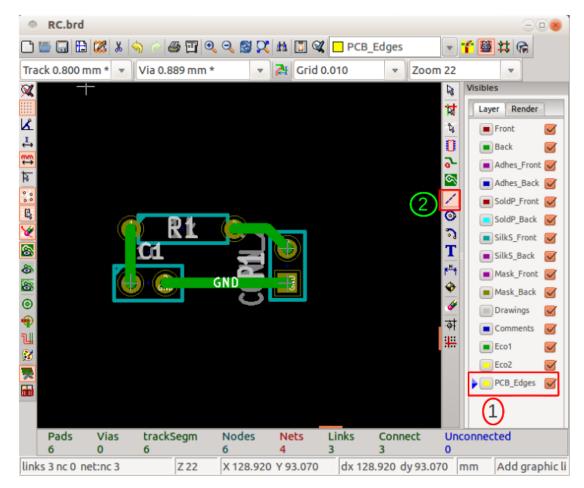

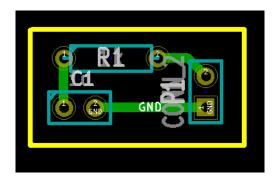

#### 4.6 Layout Editor

Open the RC\_pcb project available in Examples. Clicking on the Layout Editor tool will open Pcbnew, the layout editor used in Oscad. This shows the PCB design for RC circuit. In this window, one will create the PCB. It involves laying tracks and vias, performing optimum routing of tracks, creating one or more copper layers for PCB, etc. The PCB design for RC circuit is shown in Fig. 4.10. This is how the PCB will look like when one actually prints it on a copper-clad board. It will be saved as a .brd file in the same directory. Chapter 7 explains how to use the Layout Editor to design a PCB.

#### 4.7. SMCSim

Figure 4.9: Footprint for C1

Figure 4.10: PCB design for RC circuit

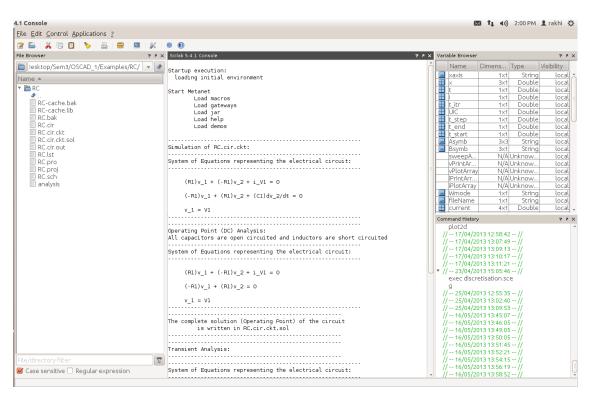

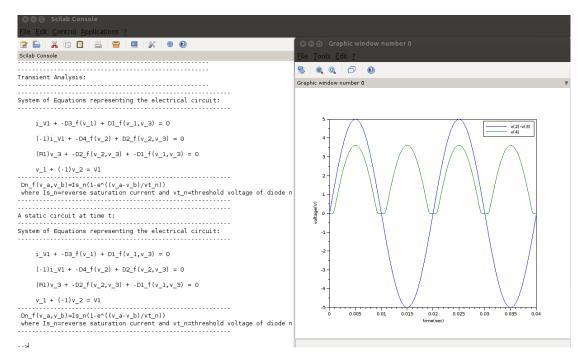

# 4.7 SMCSim

*SMCSim* stands for Scilab based Mini Circuit Simulator. This tool generates mathematical equations for the circuit, thereby giving a better understanding of the circuit. Oscad uses Scilab [3] for this purpose. Clicking on this tool will open a small window

## 4. Getting Started

Figure 4.11: System of equations representing the electrical circuit in Scilab

where one has to choose between three options: 1. Normal 2. Symbolic and 3. Matrix. The last option has been referred to as the numerical mode in this book. These are the modes used for circuit simulation. After one of them is selected and ok button is clicked, Scilab will be launched automatically. Let us choose the option Symbolic. The scilab console will show the set of equations for the circuit as shown in Fig. 4.11. A plot window opens up showing the plot of variables in the circuit. The placement of plot components in the circuit schematic determines which variables to be plotted. To know more about how to use this feature, refer to Chapter 9.

# 4.8 Model Builder

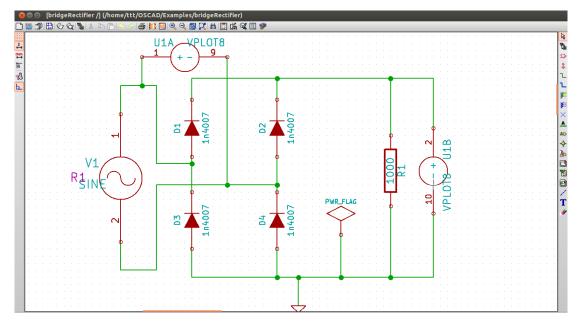

Oscad also gives an option to re-configure the model of a component. It facilitates the user to change models of components such as diode, transistor, MOSFET, etc. When one clicks on the *Model Builder* tool, the window as shown in Fig. 4.12a will appear. One sees a blank window because the RC circuit which has been opened does not have any component whose model can be edited. Let us open from the Examples folder, bridgeRectifier project which has a component with an editable model. Click on

26

#### 4.9. Subcircuit Builder

| 😣 🖻 🗈 Ngspice Model Editor        |             |                                          |

|-----------------------------------|-------------|------------------------------------------|

| File Help                         | 😣 🗐 🗐 Ngs   | pice Model Editor                        |

| 🙁 🗊 Model Select                  | File Help   | S Model Select                           |

| Please select the model OK Cancel |             | Please select the model In4007 OK Cancel |

|                                   |             |                                          |

| (a) Default appearance            | (b) Model I | Builder window of                        |

(b) Model Builder window of circuit having a diode

#### Figure 4.12: Model Builder window

| JO 1E-11 | AF 1      | EG 1.05743 | IS 7.02767e-09 | RS 0.0341512 |

|----------|-----------|------------|----------------|--------------|

| 0.5      | N 1.80803 | BV 1000    | FC 0.5         | XTI 5        |

| T 1E-07  | VJ 0.7    | IBV 5e-08  | KF 0           |              |

Figure 4.13: Model Builder window showing model of diode

the *Model Builder* tool from the Oscad toolbar. The window shown in Fig. 4.12b will appear. We can see that it shows 1n4007 in the window. After choosing 1n4007 and clicking on OK, it will respond saying Do you want to edit? After clicking on OK, a window will open. This window will contain the various parameters governing the model of diode, for example reverse breakdown voltage (BV) and ohmic resistance (RS). This is illustrated in Fig. 4.13. To know more about how to use this feature, refer to Chapter 8.

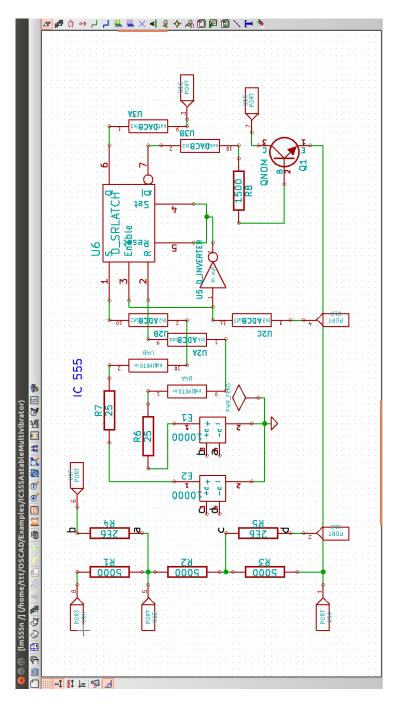

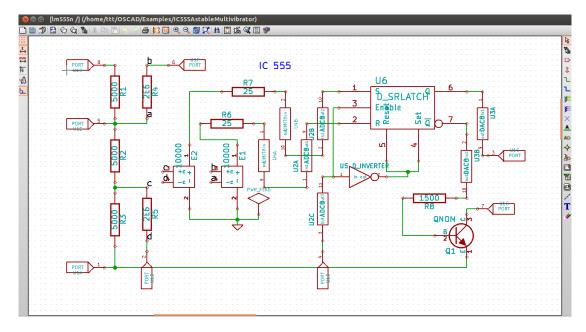

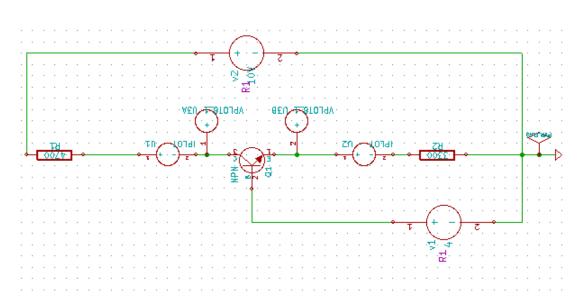

# 4.9 Subcircuit Builder

Oscad has an option to build subcircuits. The subcircuits can again have components having subcircuits and so on. This enables users to build commonly used circuits as subcircuits and then use it across circuits. For example, one can build a 12 Volt power supply as a subcircuit and then use it as just a single component across circuits without having the need to recreate it. Clicking on *Subcircuit Builder* tool will allow one to edit or create a subcircuit. To know how to make a subcircuit, refer to Chapter 8. Fig. 4.14 shows the subcircuit of 555 timer IC.

Figure 4.14: Subcircuit of 555 timer IC

# Chapter 5

# Schematic Creation

The first step in the design of an electronic system is the design of its circuit. This circuit is usually created using a Schematic Editor and is called a Schematic. Oscad uses EEschema as its schematic editor. EEschema is the schematic editor of KiCad. It is a powerful schematic editor software. It allows the creation and modification of components and symbol libraries and supports multiple hierarchical layers of printed circuit design.

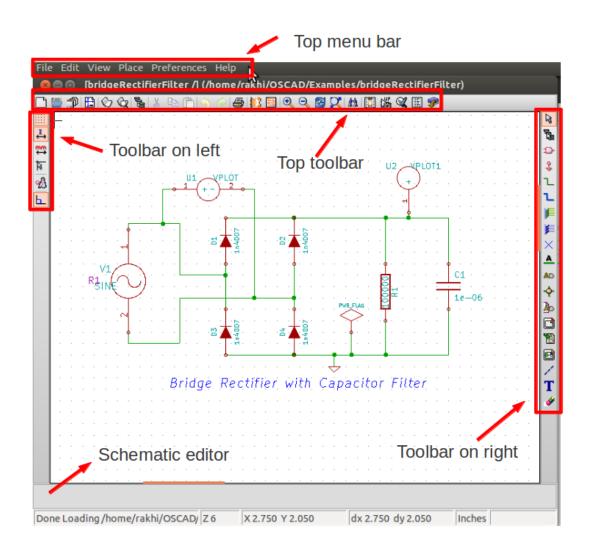

# 5.1 Familiarising the Schematic Editor interface

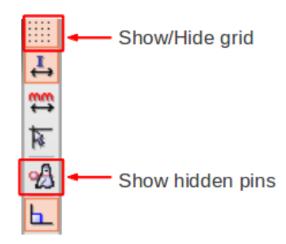

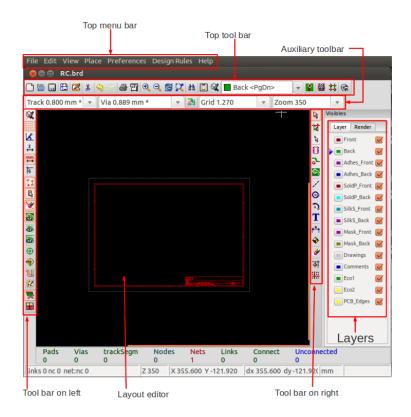

Fig. 5.1 shows the schematic editor and the various menu and toolbars. We will explain them briefly in this section.

#### 5.1.1 Top menu bar

The top menu bar will be available at the top left corner. Some of the important menu options in the top menu bar are:

- 1. File The file menu items are given below:

- (a) New Clear current schematic and start a new one

- (b) Open Open a schematic

- (c) Open Recent A list of recently opened files for loading

- (d) Save Whole Schematic project Save current sheet and all its hierarchy.

- (e) Save Current Sheet Only Save current sheet, but not others in a hierarchy.

- (f) Save Current sheet as Save current sheet with a new name.

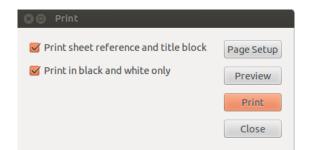

- (g) Print Access to print menu (See Fig. 5.2).

- (h) Plot Plot the schematic in Postscript, HPGL, SVF or DXF format

- (i) Quit Quit the schematic editor.

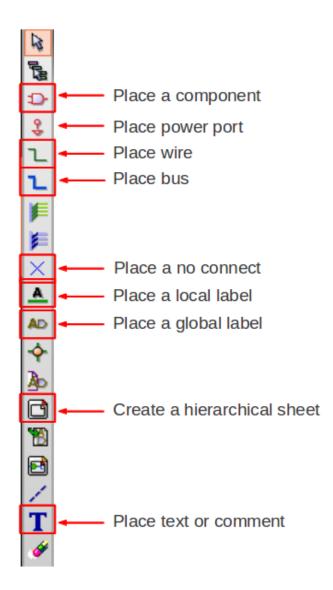

- 2. Place The place menu has shortcuts for placing various items like components, wire and junction, on to the schematic editor window. See Sec. 5.1.5 to know

Figure 5.1: Schematic editor with the menu bar and toolbars marked

more about various shortcut keys (hotkeys).

- 3. Preferences The preferences menu has the following options:

- (a) Library Select libraries and library paths

- (b) Colors Select colors for various items.

- (c) Options Display schematic editor options (Units, Grid size).

- (d) Language Shows the current list of translations. Use default.

- (e) Hotkeys Access to the hot keys menu. See Sec. 5.1.5 about hotkeys.

- (f) Read preferences Read configuration file.

#### 5.1. Familiarising the Schematic Editor interface

Figure 5.2: Print options

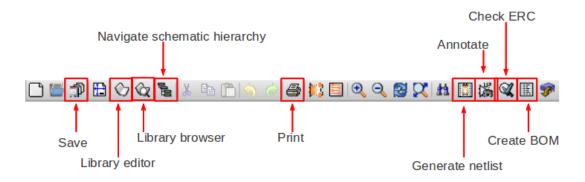

Figure 5.3: Toolbar on top with important tools marked

(g) Save preferences - Save configuration file.

#### 5.1.2 Top toolbar

Some of the important tools in the top toolbar are discussed below. They are marked in Fig. 5.3.

- 1. Save Save the current schematic

- 2. Library Editor Create or edit components. See Sec. 5.2 for more details.

- 3. Library Browser Browse through the various component libraries available

- 4. Navigate schematic hierarchy Navigate among the root and sub-sheets in the hierarchy

- 5. Print Print the schematic

- 6. Generate netlist Generate a netlist for PCB design or for simulation.

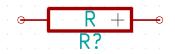

- 7. Annotate Annotate the schematic