**TITLE** : Design of 12-Bit DAC Using CMOS Technology

**STUDENT NAME**: Thirlojanan U

**COLLEGE NAME**: Sri Eshwar College of Engineering, Coimbatore.

## PROBLEM STATEMENT:

Design and simulate a 12-bit CMOS DAC in eSim such that it provides high resolution, low power dissipation, and minimum non-linearity errors. The DAC should efficiently convert a 12-bit digital input into a proper analog voltage output with optimized speed, accuracy, and power dissipation for practical applications.

## **ABSTRACT:**

A Digital-to-Analog Converter (DAC) is employed to generate the corresponding analog output signals from the digital input signals. In the proposed project, a 12-bit R-2R ladder-based DAC is designed and examined for effective functionality with low power consumption and low non-linearity errors. The DAC is simulated using eSim software with a CMOS-based design. The central components are an operational amplifier and an R-2R ladder network. The op-amp has a two-stage design, which is a high-gain differential amplifier for the first stage and a common-source amplifier to enhance output swing and overall performance in the second stage. In this project, our goal is to create an optimized and compact DAC design for high-precision systems.

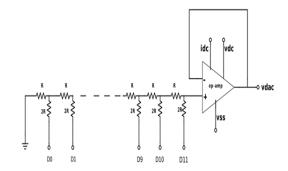

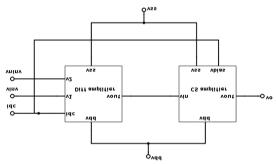

## **PROPOSED CIRCUIT:**

Fig 1: Implementation of 12-bit R-2R DAC

Fig 2: Schematic of op-amp

## **SOURCE/REFERENCES:**

- 1)Tutorial: Digital to Analog Conversion The R-2R DAC, Alan Wolke, May 2013.

- 2) Anshul Agarwal, Design of Low Power 8-Bit Digital-to-Analog Converter with Good Voltage-Stability, Center for VLSI and Embedded System Technologies International Institute of Information Technology Hyderabad, India May 2013.