# FET Based Master Slave Negative Edge Triggered Flipflop Using Sky130PDK

### **Theory:**

A negative-edge triggered D type master-slave flip-flop consists of a pair of D-latches, positive latch (master) and negative latch (slave) connected in series. The latches are designed using mux by giving feedback from output to one of the inputs of 2:1 mux in. The mux is constructed using the transmission gates. The transmission gate is a bidirectional circuit which is made by connecting the pfet and nfet in parallel. The clock is given to the select lines of the mux so that the entire circuit behaves as the master slave negative edge triggered flipflop. During the high level of the clock, the master samples the input and the slave retains the previous output through feedback. At low level of the clock, the slave will go to transparent mode and samples the output of the master and the master will go to the hold mode, retaining the previous value. Thus, the output of master slave negative edge triggered flipflop changes once in one clock cycle during the high to low transition of clock. The transistors for designing all the circuits were used form the **SKY130PDK library** in eSim.

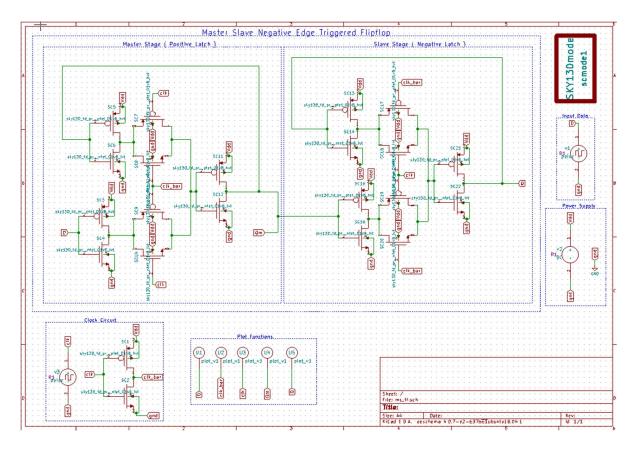

### Schematic Diagram:

The circuit schematic of the FET based master slave negative edge triggered flipflop using sky130pdk in eSim is as shown below:

Figure 1: Schematic of the Master Slave Negative Edge Triggered Flipflop

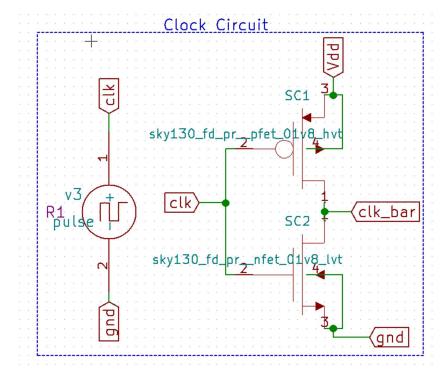

Figure 2: Clock Circuit

# **Simulation Results:**

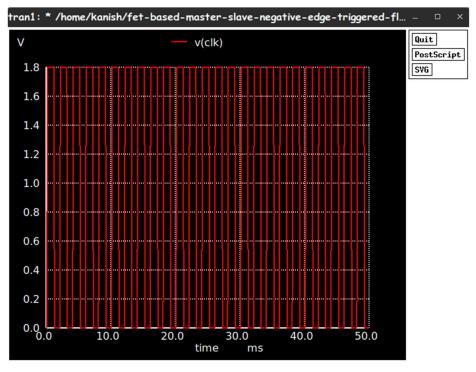

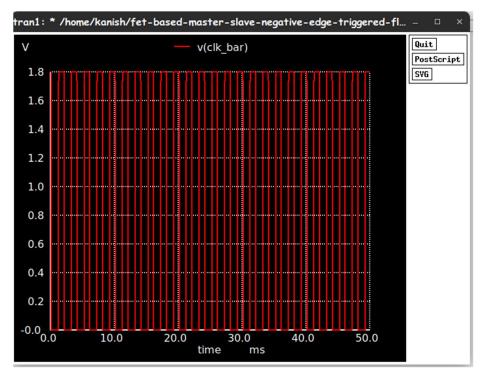

1. Ngspice Plots:

Figure 3: Clock Signal

Figure 4: Clock bar Signal

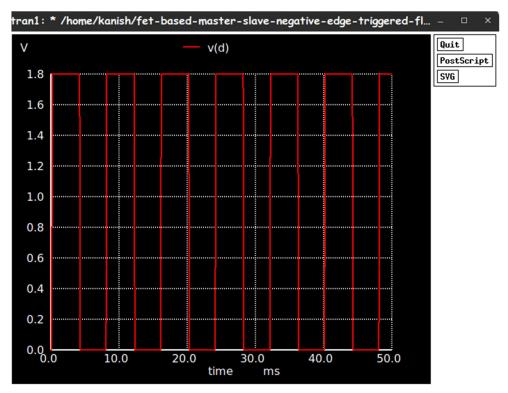

Figure 5: Input Data (D)

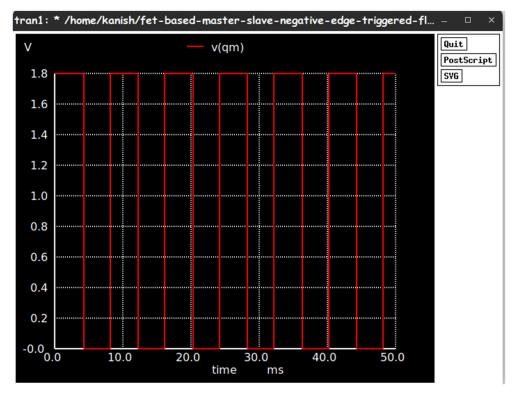

Figure 6: Master Output

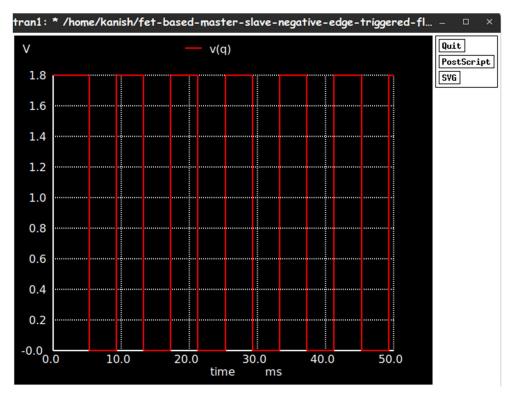

Figure 7: Master Slave Negative Edge Triggered Flipflop Output

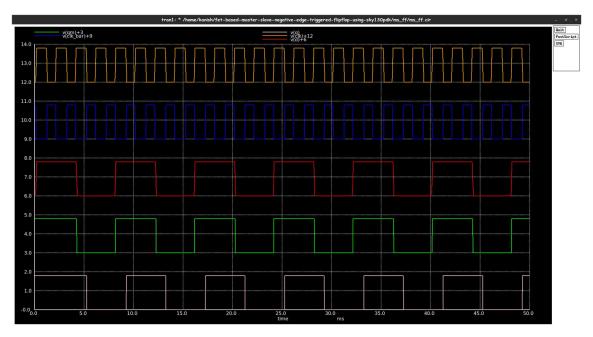

Figure 8: Combined Waveforms of the Master Slave Negative Edge Triggered Flipflop using SKY130PDK

#### 2. Netlist

Figure 9: Netlist

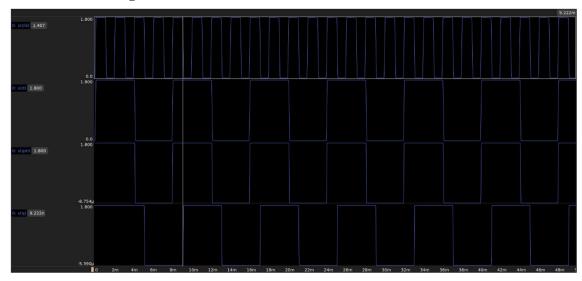

3. GAW - Gtk Analog Wave viewer Plot

Figure 10: Combined Waveform in GTK Analog Viewer

## **Conclusion:**

Thus, we have implemented the FET based master slave negative edge triggered flipflop using Sky130PDK in eSim and the appropriate waveforms are obtained.

# **References:**

- Morris Mano & Michael D Ciletti, "Digital Design: With an Introduction to Verilog HDL, 5th Edition, Pearson Education, 2013

- Neil H.E. Weste, David Money Harris —CMOS VLSI Design: A Circuits and Systems Perspective.

- <u>https://www.sciencedirect.com/topics/computer-science/master-slave-flip#:~:text=A%20negative%2Dedge%20triggered%20D,edge%20of%20the%20clock%20pulse</u>.

- 4. https://skywater-pdk.readthedocs.io/en/main/