## **Analysis Of Full Subtractor**

R. Arun Sir C R Reddy College of Engineering, Eluru, Andhra Pradesh

<u>Abstract:</u> - A full subtractor is a combinational circuit which performs the subtraction of the three input variables. It is designed using the logic gates AND, NOT, OR and XOR. It has three inputs A, B and C which represent the minuend, subtrahend and the previous borrow. The two outputs D and Bo represent the difference and borrow.

**Full subtractor:** - subtractor an electronic logic circuit for calculating the difference between two binary numbers, the minuend and the number to be subtracted, the subtrahend. A *full subtractor* performs this calculation with three inputs: minuend bit, subtrahend bit, and borrow bit. It produces two outputs: the difference and the borrow. Full subtractors thus allow for the inclusion of borrows generated by previous stages of subtraction when forming their output signals, and can be cascaded to form *n*-bit subtractors. Alternatively, the subtract operation can be performed using two *half subtractors*, which are simpler since they contain only two inputs and produce two outputs.

| Inputs |   |                      | Outputs |        |

|--------|---|----------------------|---------|--------|

| Α      | В | Borrow <sub>in</sub> | Diff    | Borrow |

| 0      | 0 | 0                    | 0       | 0      |

| 0      | 0 | 1                    | 1       | 1      |

| 0      | 1 | 0                    | 1       | 1      |

| 0      | 1 | 1                    | 0       | 1      |

| 1      | 0 | 0                    | 1       | 0      |

| 1      | 0 | 1                    | 0       | 0      |

| 1      | 1 | 0                    | 0       | 0      |

| 1      | 1 | 1                    | 1       | 1      |

## Table1: Truth table of full subtractor

From Table 1 the difference and borrow bits of the output can be obtained as Difference.

D = A'B'C + A'BC' + AB'C' + ABC (difference)

Br = A 'B 'C + A 'BC' + A 'BC+ ABC (borrow)

**Reference**: Dondapati Naresh,V.B.Gopala Krishna,"Design and Implementation of Fault Tolerant Carry Skip Adder or Subtractor using Reversible Logic Gates", ISSN 2322-0929 Vol.02, Issue.07, October-2014.

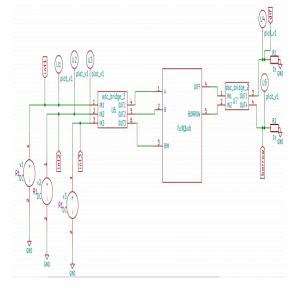

Fig1: Implemented circuit

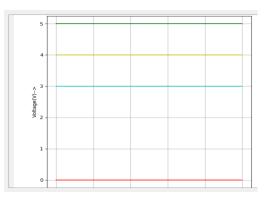

Fig3: Implemented waveforms