# **Octal to Binary Encoder**

Parth Deshpande BITS Pilani, KK Birla Goa Campus 8 April 2022

#### **Abstract**

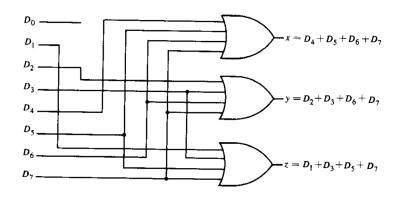

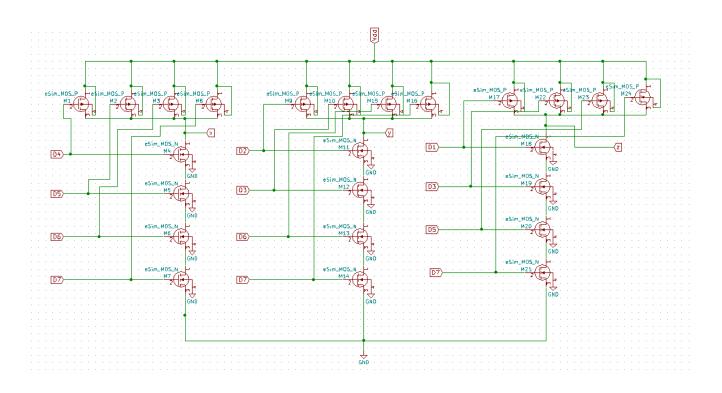

The goal of the design is to make an encoder that will have input as an octal number with 8 bits and the output will be its binary form with 3 bits. The design will use CMOS technology to make NAND gates that will be used in making the encoder.

#### **Keywords**

Encoder, octal, binary, CMOS, NAND

#### Introduction

In digital domain, encoders are an important part of the circuit. They are useful in converting data from one form to another. It can also be useful in transmitting data in easier ways.

This is the basic schematic of an encoder. The input will 2<sup>N</sup> bits and the output will be N bits.

#### **Truth Table**

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |   |   |   |   |   |   |   |

|------------------------------------------------------|---|---|---|---|---|---|---|

| 1                                                    | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0                                                    | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0                                                    | 0 | 1 | 0 | 0 | 0 | 0 | Ō |

| 0                                                    | 0 | 0 | 1 | 0 | 0 | 0 | Ö |

| 0                                                    | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 0                                                    | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 0                                                    | 0 | 0 | 0 | 0 | Ó | 1 | 0 |

| 0                                                    | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| O | utp | uts |

|---|-----|-----|

|   |     |     |

| X | у | Z |

|---|---|---|

| 1 | 1 | 1 |

| 1 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 0 | 0 |

| 0 | 1 | 1 |

| 0 | 1 | 0 |

| 0 | 0 | 1 |

| 0 | 0 | 0 |

The output is in the active-low format. This is due to NAND gates used in the circuit design.

## Circuit

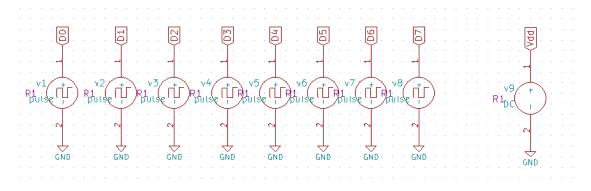

D0-D7 are the inputs. Vdd is the power source.

## **Plots**

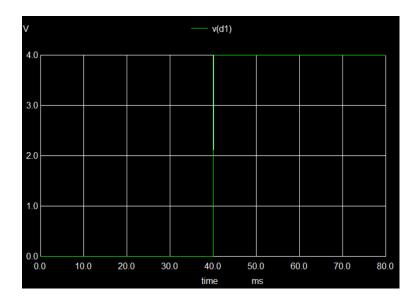

When the input is 01000000 (only D1 is high)

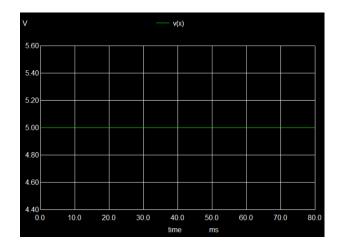

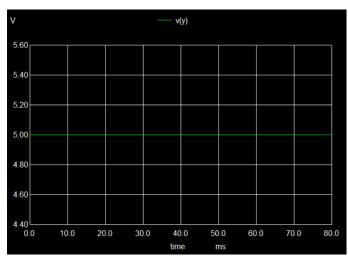

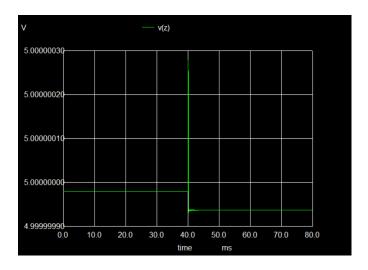

The expected output is xyz = 110 (according to truth table)

As it can be seen x and y outputs are always high, while z output goes low after 40ms mark. The exact voltage to 0 is not obtained due difficulty getting appropriate aspect ratios.

Similar results can be obtained for every octal number.

### References

[1] B Razavi *Design of Analog CMOS Integrated Circuits*" Tata Mcgraw Hill, 2002

[2] Morris Mano *Digital Design* "Prentice Hall 1995