# **Circuit Simulation Project**

https://esim.fossee.in/circuit-simulation-project

Name of Participant: UTUKURI GEYARKA S NIKHILESH

Project Guide: Dr. MAHESWARI. R

Title of the Project: -

# **Design of XOR gate using NAND gates**

# Theory/Description: -

XOR gate (sometimes EOR, or EXOR and pronounced as Exclusive OR) is a digital logic gate that gives a true (1 or HIGH) output when the number of true inputs is odd.

An XOR gate implements an exclusive or  $A \bigoplus B$  from mathematical logic; that is, a true output results if one, and only one, of the inputs to the gate is true. If both inputs are false (0/LOW) and both are true, a false output results.

XOR represents the inequality function, i.e., the output is true if the inputs are not alike otherwise the output is false. XOR can also be viewed as addition modulo 2.

As a result, XOR gates are used to implement binary addition in computers. XOR is used in adders, subtractors, comparators, and controlled inverters. XOR gate can be implemented by only using the universal gates like only NAND gates or only NOR gates.

#### Truth Table for XOR Gate:

| Α | В | A XOR B<br>(A ⊕ B) |

|---|---|--------------------|

| 0 | 0 | 0                  |

| 0 | 1 | 1                  |

| 1 | 0 | 0                  |

| 1 | 1 | 1                  |

Here, A, B are inputs and A XOR B or  $(A \oplus B)$  is output.

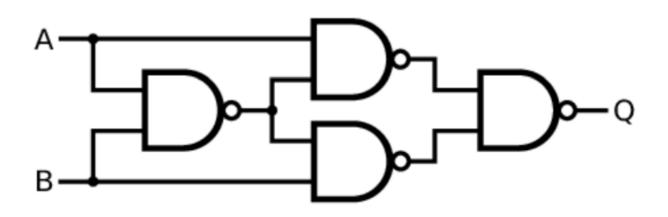

Circuit for Xor gate using Nand gates:

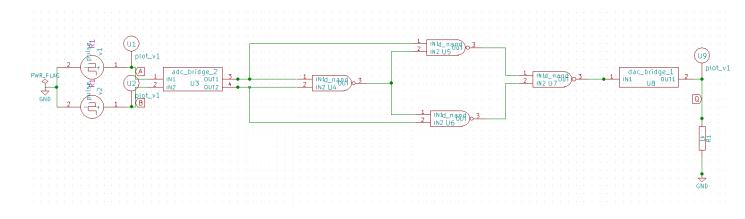

# Schematic Diagram:

The circuit schematic for XOR gate using NAND gates in eSim is as shown below:

#### Source details:

| Analysis                           | Source Details      | NgSpice Model | Device Modeling | Subcircuits |    |

|------------------------------------|---------------------|---------------|-----------------|-------------|----|

| Add parameters for pulse source v1 |                     |               |                 |             |    |

| Enter initial value(Volts/Amps):   |                     |               |                 |             | 0  |

| Enter p                            | ulsed value(Volts/A | mps):         |                 |             | 5  |

| Enter d                            | elay time (seconds) | :             |                 |             | 10 |

| Enter ri                           | se time (seconds):  |               |                 |             | 0  |

| Enter fa                           | all time (seconds): |               |                 |             | 0  |

| Enter p                            | ulse width (seconds | ):            |                 |             | 10 |

| Enter p                            | eriod (seconds):    |               |                 |             | 20 |

| Add parameters for pulse source v2  Enter initial value(Volts/Amps): | 0  |

|----------------------------------------------------------------------|----|

| Enter pulsed value(Volts/Amps):                                      | 5  |

| Enter delay time (seconds):                                          | 5  |

| Enter rise time (seconds):                                           | 0  |

| Enter fall time (seconds):                                           | 0  |

| Enter pulse width (seconds):                                         | 5  |

| Enter period (seconds):                                              | 10 |

#### Analysis:

| Transient Analysis |    |         |  |  |  |

|--------------------|----|---------|--|--|--|

| Transient Analysis | 0  | Sec 🗸 🗸 |  |  |  |

| Step Time          | 10 | ms      |  |  |  |

| Stop Time          | 20 | Sec 💌   |  |  |  |

|                    |    |         |  |  |  |

# Simulation Results :

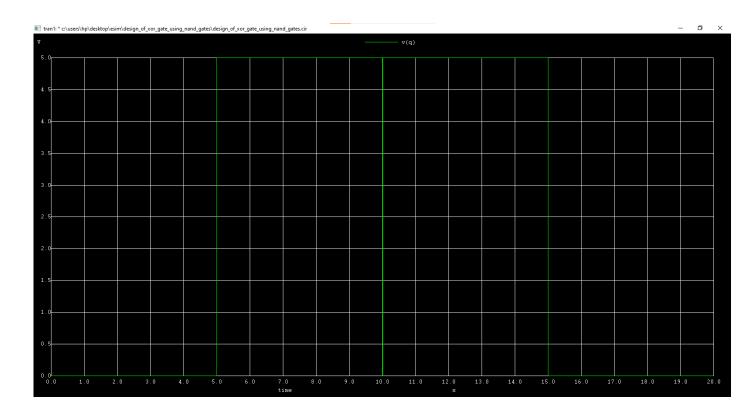

# 1) Ngspice plots:

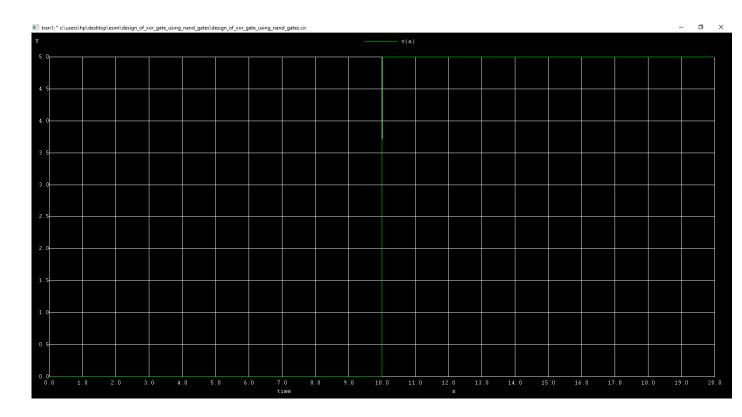

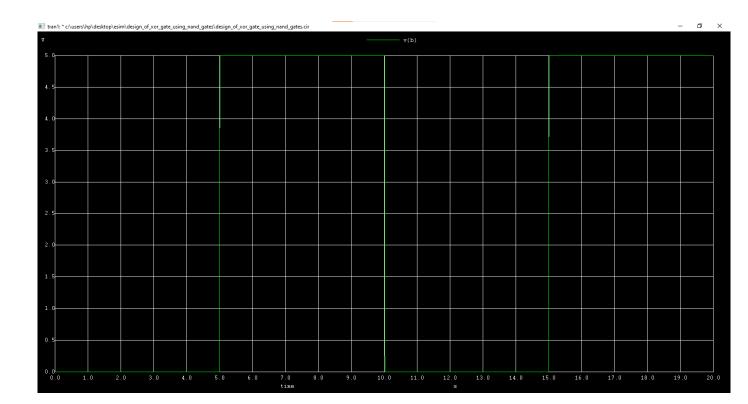

### Input waveforms:

<u>A:</u>

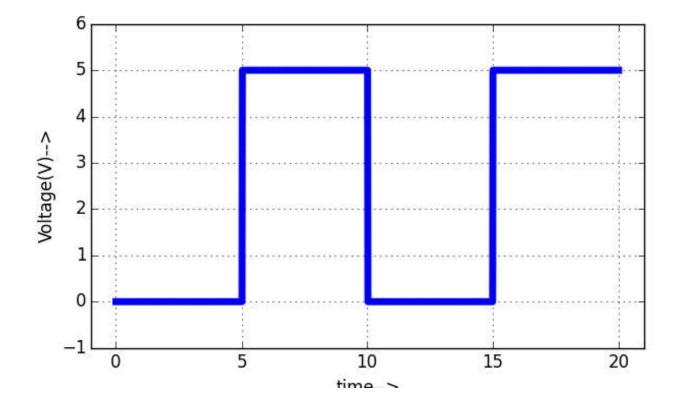

<u>B:</u>

### **Output Waveforms:**

# <u>Q (A⊕B):</u>

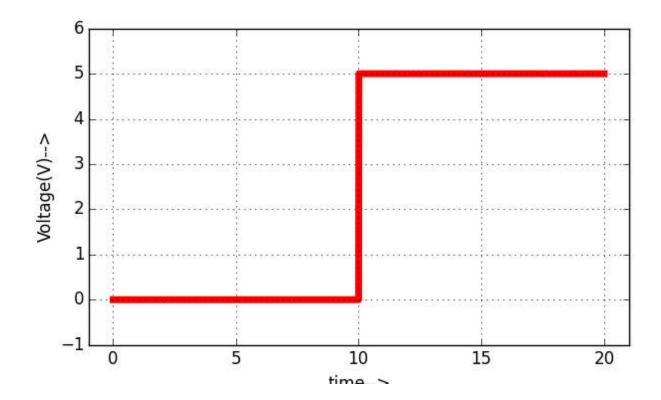

# 2) Python plots:

# Input waveforms:

<u>A:</u>

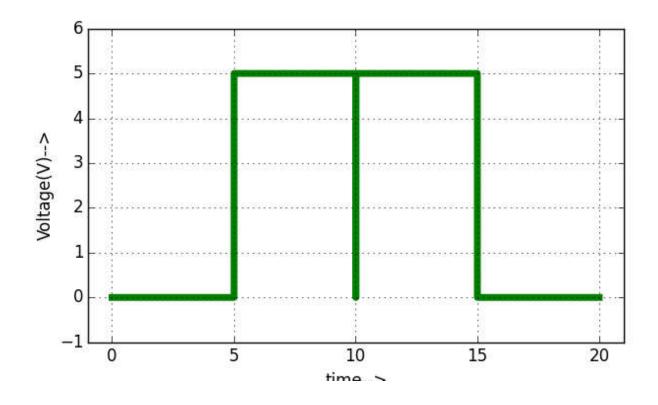

#### **Output waveforms:**

#### <u>Q (A⊕B):</u>

# **Conclusion:**

Thus, we have studied the design of Xor gate using Nand gates using eSim and we get the appropriate waveforms.

### **References:**

https://www.engineersgarage.com/vhdl-tutorial-7-nand-gate-as-universalgate-using-vhdl/