# **Circuit Simulation Project**

https://esim.fossee.in/circuit-simulation-project

Name of the Participant: Anuj Singh Chauhan

Project Guide: Dr R. Maheshwari

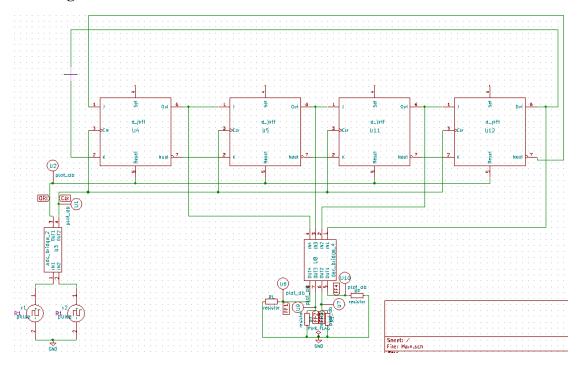

Title of the circuit: 4-Bit Mod-8 Johnson Counter Using J-K Flip Flop

### Theory:

A Johnson counter, also known as twisted ring counter or walking ring counter, is a shift register in which the complement of the output of the last register is given as the input of the first register and circulates a stream of ones followed by zeros around the ring.

For example after every clock cycle the parallel output of the counter is as follows:

0000, 1000, 1100, 1110, 1111, 0111, 0011, 0001, 0000

As there are only 8 distinct states hence it's a Mod -8 counter.

In this project I have implemented Mod-8 Johnson counter using 4 J-K flip flops. So to make the J-K flip flop act like D flip flop we have to give the input to J and complement of the input to K. By using this principal I constructed this Mod-8 Twisted Ring Counter.

#### **Circuit Diagram:**

## **Results:**

| Add parameters for pulse source v2                      |    |

|---------------------------------------------------------|----|

| Enter initial value(Volts/Amps):                        | 0  |

| Enter pulsed value(Volts/Amps):                         | 5  |

| Enter delay time (seconds):                             | 5  |

| Enter rise time (seconds):                              | 0  |

| Enter fall time (seconds):                              | 0  |

| Enter pulse width (seconds):                            | 5  |

| Enter period (seconds):                                 | 10 |

| Add parameters for pulse source v1                      |    |

| Enter initial value(Volts/Amps):                        | 5  |

| Enter pulsed value(Volts/Amps):                         |    |

|                                                         | 0  |

| Enter delay time (seconds):                             | 5  |

|                                                         | -  |

| Enter delay time (seconds):                             | 5  |

| Enter delay time (seconds):  Enter rise time (seconds): | 5  |

Fig 1: Source Details

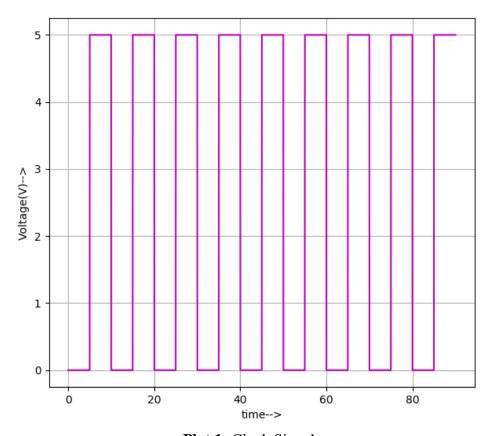

Plot 1: Clock Signal

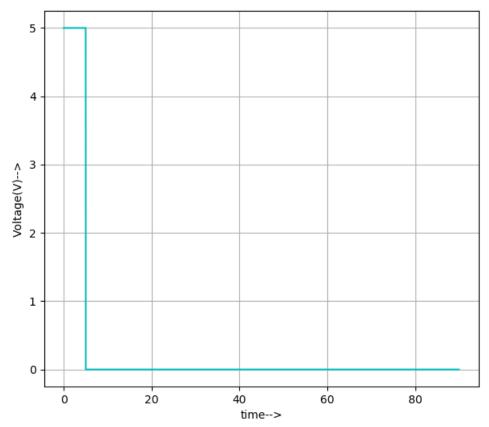

Plot 2: Orientation Signal

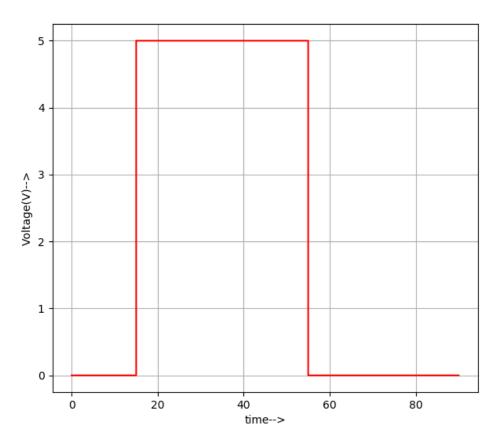

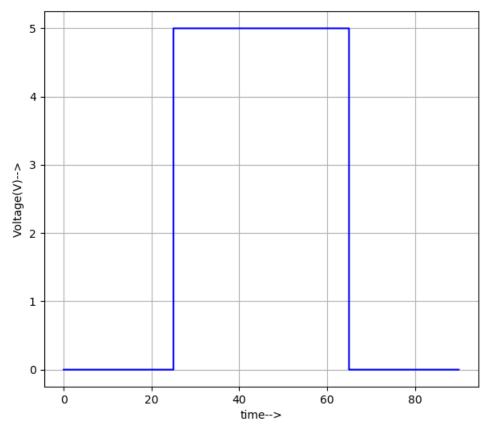

**Plot 3:** Output of Flip Flop 1

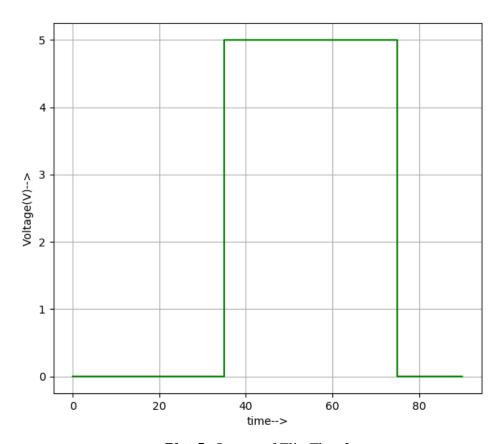

**Plot 4:** Output of Flip Flop 2

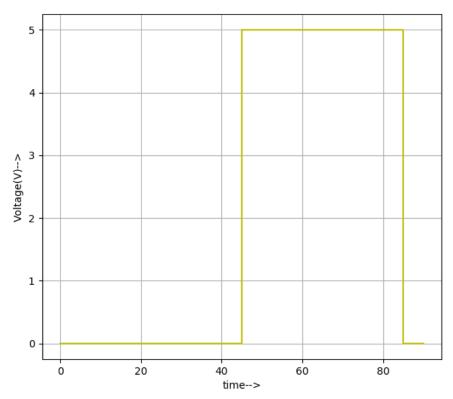

**Plot 5:** Output of Flip Flop 3

**Plot 6:** Output of Flip Flop 4

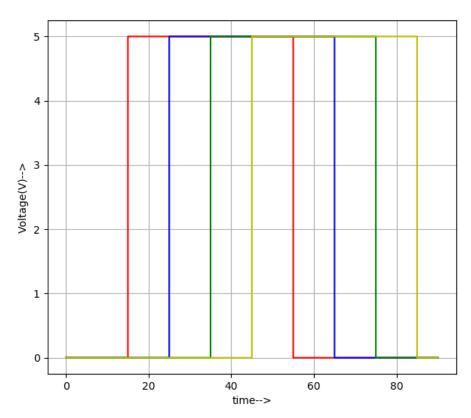

**Plot 7:** Output of All the Flip Flops

Hence the pattern formed here is 0000, 1000, 1100, 1110, 1111, 0111, 0011, 0001, and 0000.

## **Source/Reference(s):**

https://www.geeksforgeeks.org/n-bit-johnson-counter-in-digital-logic/

https://www.electronics-tutorials.ws/sequential/seq\_6.html