## **Circuit Simulation Project**

https://esim.fossee.in/circuit-simulation-project

Name of the participant: SHREYAS BHASKAR

Project guide: Dr. Maheswari. R

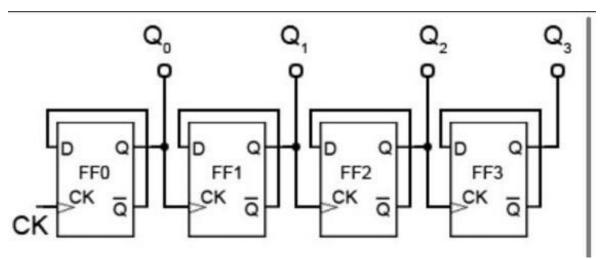

Title of the circuit: 4 Bit Asynchronous DOWN Counter Using D Flip Flop

### **Theory/Description:**

A 4-bit asynchronous DOWN counter is shown in above diagram. It is simple modification of the UP counter. 4-bit DOWN counter will count numbers from 15 to 0, downwards. The clock inputs of all flip flops are cascaded and the D input (DATA input) of each flip flop is connected to logic 1.

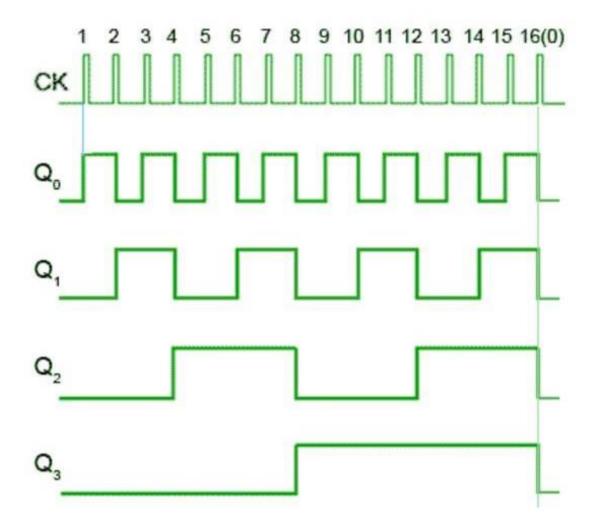

That means the flip flops will toggle at each active edge (positive edge) of the clock signal. The clock input is connected to first flip flop. The other flip flops in counter receive the clock signal input from Q output of previous flip flop, rather than Q' output.

Here Q0, Q1, Q2, Q3 represents the count of the 4-bit down counter. The output of the first flip flop will change, when the positive edge of clock signal occurs. For example, if the present count = 3, then the up counter will calculate the next

count as 2. The input clock will cause the change in output (count) of the next flip-flop.

The operation of down counter is exactly opposite to the up-counter operation. Here every clock pulse at the input will reduce the count of the individual flip flop. So, the down counter counts from 15, 14, 13...0 i.e. (0 to 1510) or 11112 to 00002.

Both up and down counters are designed using the asynchronous, based on clock signal, we don't use them widely, because of their unreliability at high clock speeds.

As asynchronous counters are formed by connecting flip-flops together and any number of flip-flops can be connected or "cascaded" together to form a "divide-by-n" binary counter, the modulo's or "MOD" number still applies as it does for asynchronous counters so a Decade counter or BCD counter with counts from 0 to  $2^{n}-1$  can be built along with truncated sequences.

For the 4-bit counter, we require 4 flip flops and we can generate  $2^4 = 16-1=15$  states and count (1111 1110 ... 0000).

### Circuit diagram:

## **Output:**

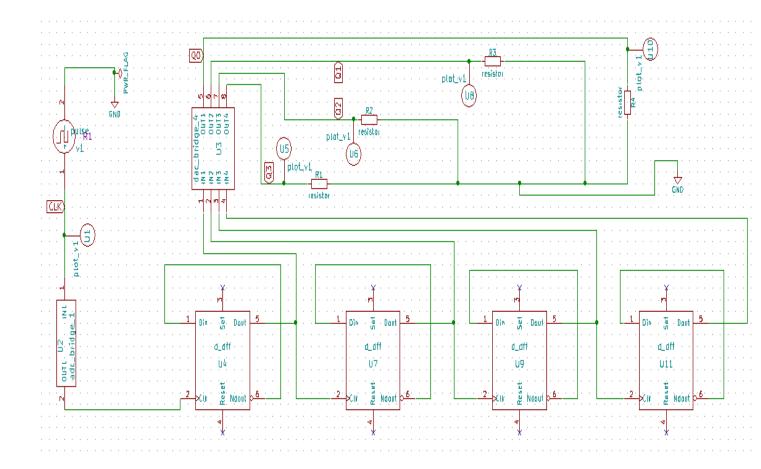

Esim circuit design:

# Output [Ngspice]:

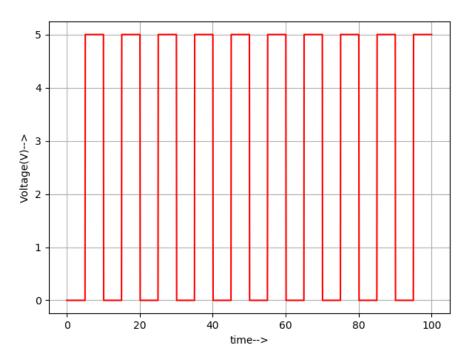

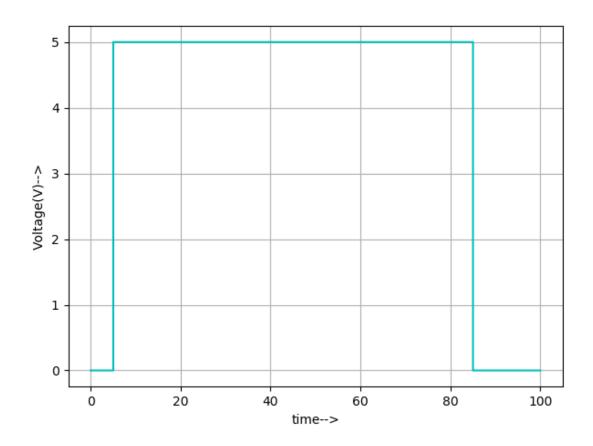

<u>CLK</u>

# Output [python plot]:

# <u>CLK</u>

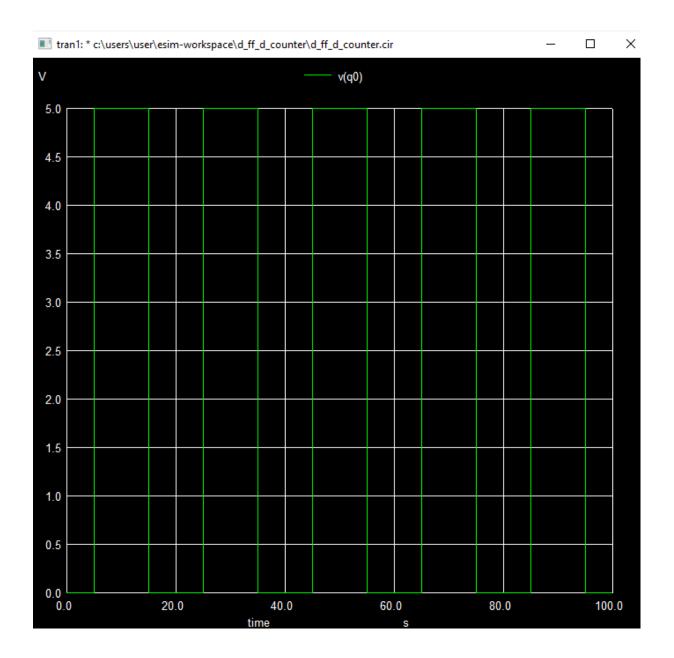

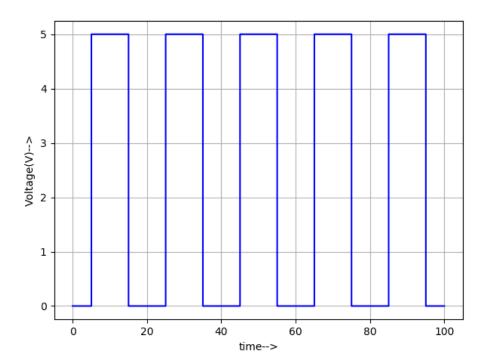

<u>Q0</u>

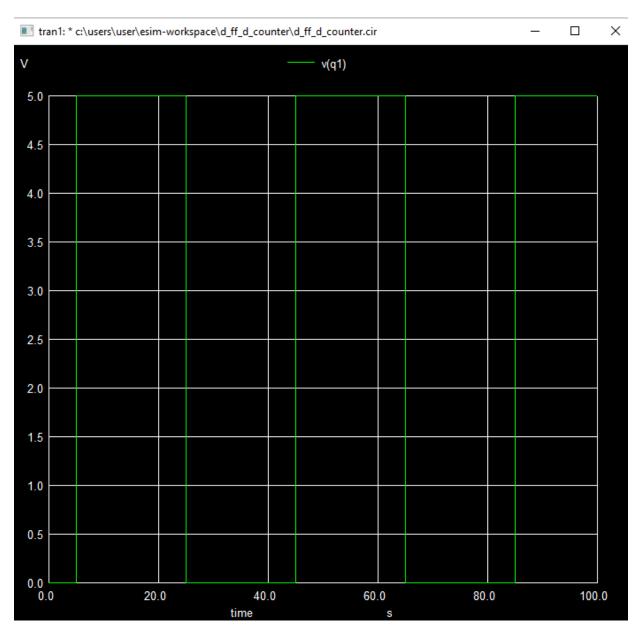

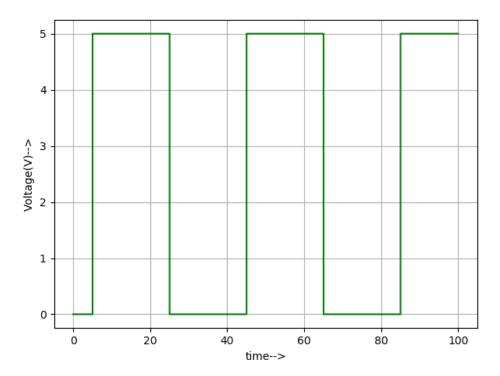

<u>Q1</u>

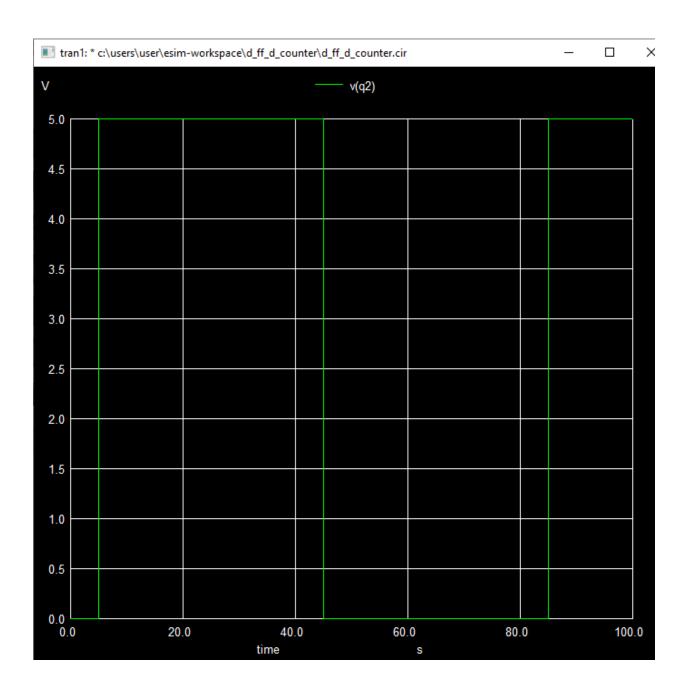

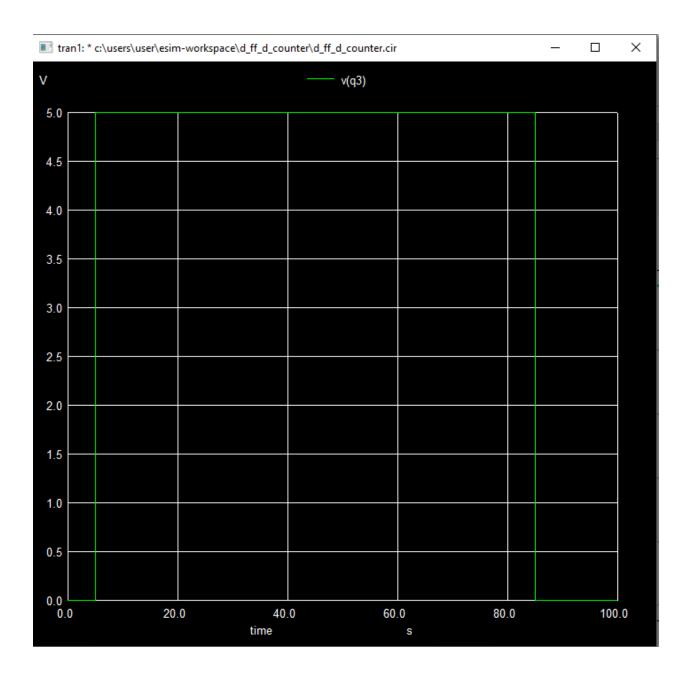

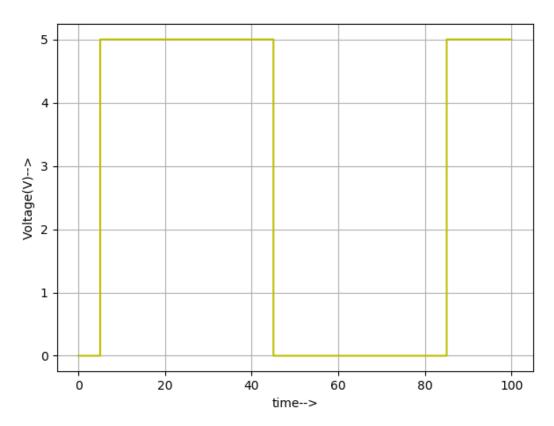

<u>Q2</u>

# **REFERENCES:**

https://www.geeksforgeeks.org/asynchronous-down-counter/