# **CIRCUIT SIMULATION PROJECT**

https://esim.fossee.in/circuit-simulation-project

Name of the participant: Sam Meshach D

Project Guide: Dr. Maheswari. R

## Title of the circuit:

# **2 - BIT MAGNITUDE COMPARATOR**

#### THEORY/DESCRIPTION:

A magnitude digital Comparator is a combinational circuit that compares two digital or binary numbers to find out whether one binary number is equal, less than or greater than the other binary number.

A comparator used to compare two binary numbers each of two bits is called a 2-bit Magnitude comparator. It consists of four inputs and three outputs to generate less than, equal to and greater than

between two binary numbers.

|    | INPUT |           |    |                                              | OUTPUT |     |  |

|----|-------|-----------|----|----------------------------------------------|--------|-----|--|

| A1 | AO    | <b>B1</b> | BO | A <b< th=""><th>A=B</th><th>A&gt;B</th></b<> | A=B    | A>B |  |

| 0  | 0     | 0         | 0  | 0                                            | 1      | 0   |  |

| 0  | 0     | 0         | 1  | 1                                            | 0      | 0   |  |

| 0  | 0     | 1         | 0  | 1                                            | 0      | 0   |  |

| 0  | 0     | 1         | 1  | 1                                            | 0      | 0   |  |

| 0  | 1     | 0         | 0  | 0                                            | 0      | 1   |  |

| 0  | 1     | 0         | 1  | 0                                            | 1      | 0   |  |

| 0  | 1     | 1         | 0  | 1                                            | 0      | 0   |  |

| 0  | 1     | 1         | 1  | 1                                            | 0      | 0   |  |

| 1  | 0     | 0         | 0  | 0                                            | 0      | 1   |  |

| 1  | 0     | 0         | 1  | 0                                            | 0      | 1   |  |

| 1  | 0     | 1         | 0  | 0                                            | 1      | 0   |  |

| 1  | 0     | 1         | 1  | 1                                            | 0      | 0   |  |

| 1  | 1     | 0         | 0  | 0                                            | 0      | 1   |  |

| 1  | 1     | 0         | 1  | 0                                            | 0      | 1   |  |

| 1  | 1     | 1         | 0  | 0                                            | 0      | 1   |  |

| 1  | 1     | 1         | 1  | 0                                            | 1      | 0   |  |

The truth table for a 2-bit comparator is given below:

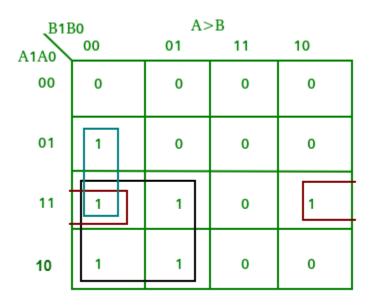

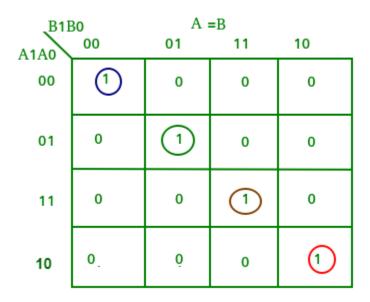

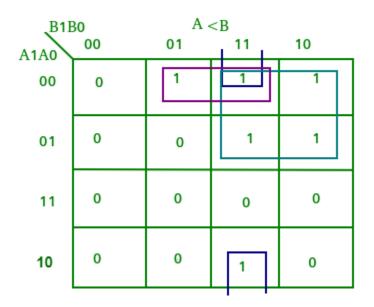

From the above truth table K-map for each output can be drawn as

follows:

From the above K-maps logical expressions for each output can be expressed as follows:

A>B: A1B1' + A0B1'B0' + A1A0B0'

A=B: A1'A0'B1'B0' + A1'A0B1'B0 + A1A0B1B0 + A1A0'B1B0'

: A1'B1' (A0'B0' + A0B0) + A1B1 (A0B0 + A0'B0')

: (A0B0 + A0'B0') (A1B1 + A1'B1')

: (A0 Ex-nor B0) (A1 Ex-nor B1)

A<B: A1'B1 + A0'B1B0 + A1'A0'B0

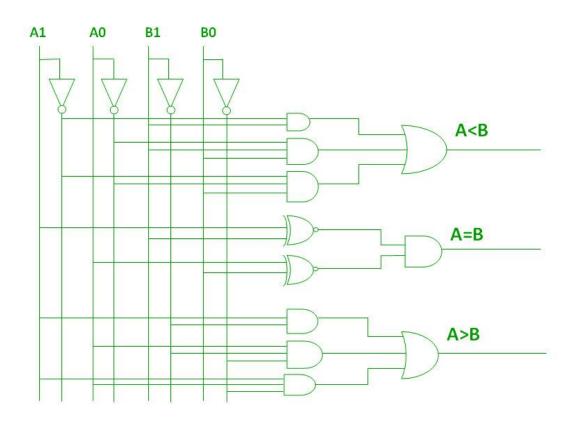

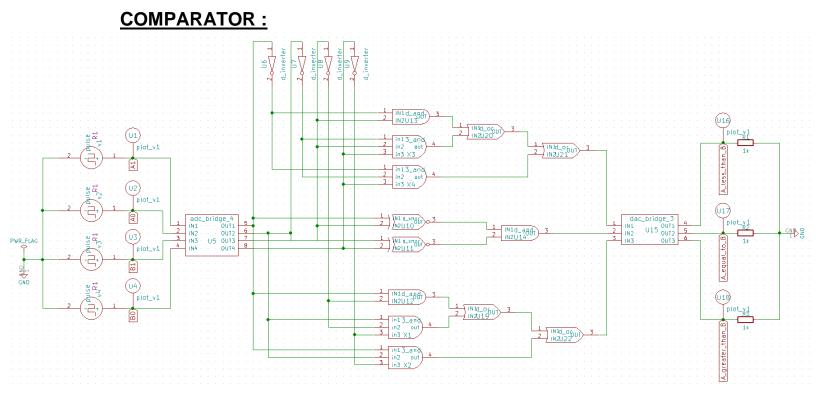

By using these Boolean expressions, we can implement a logic circuit

for this comparator as given below:

#### **ESIM CIRCUIT DIAGRAM FOR 2 - BIT MAGNITUDE**

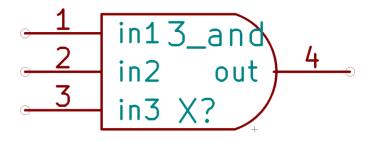

#### Subcircuit Symbol for 3-Input AND Gate (already exists in

eSim\_Subckt)

#### **RESULT/OUTPUT:**

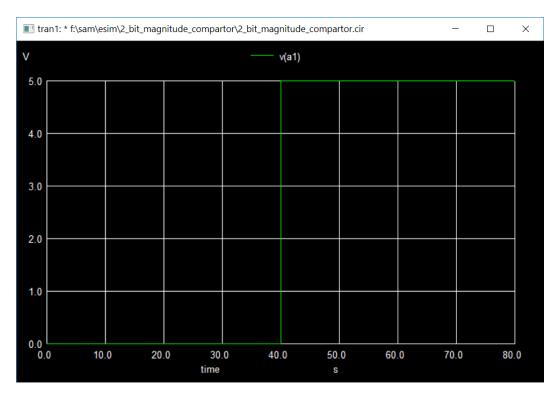

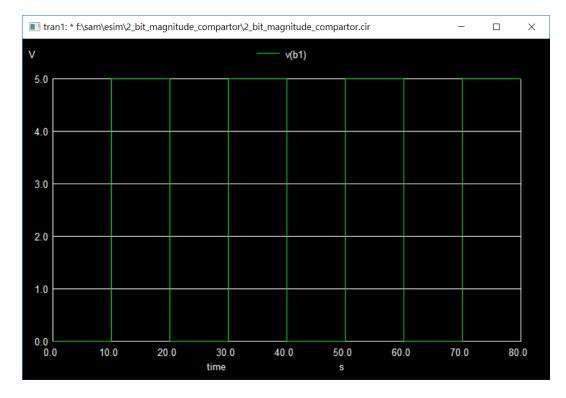

• **NGSPICE PLOTS:**

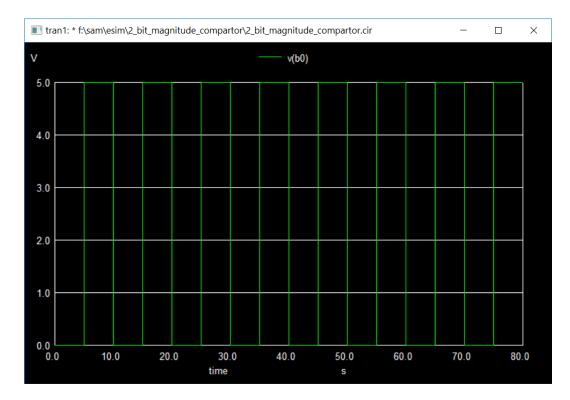

#### **INPUTS:**

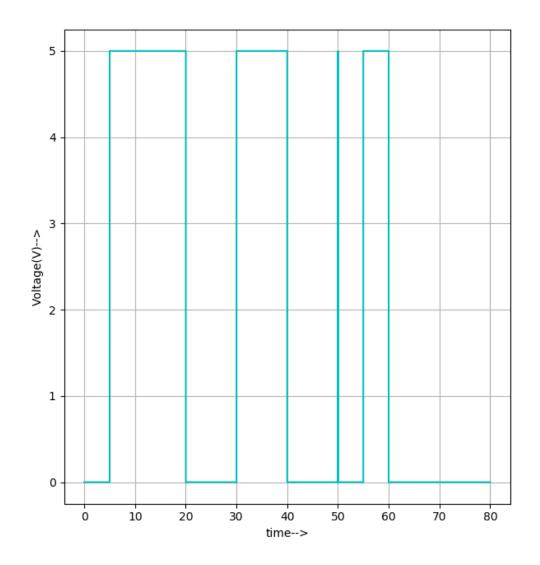

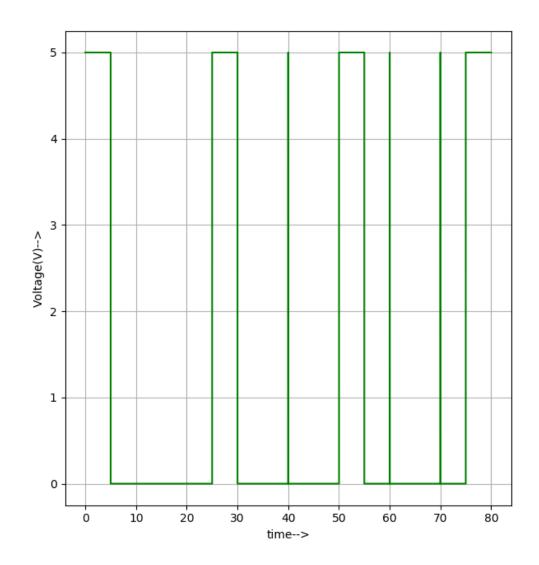

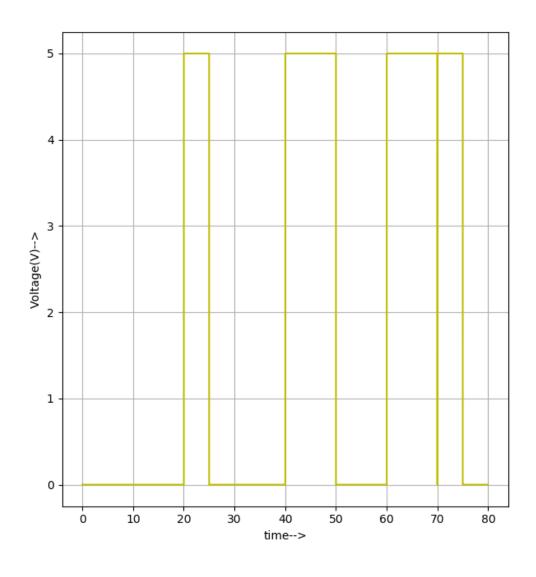

**B0**

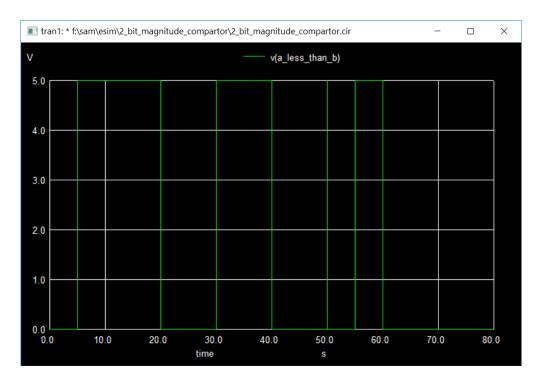

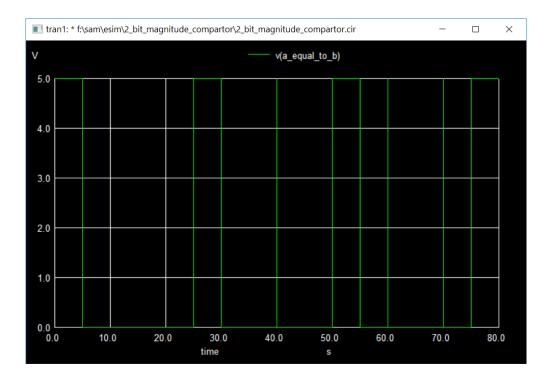

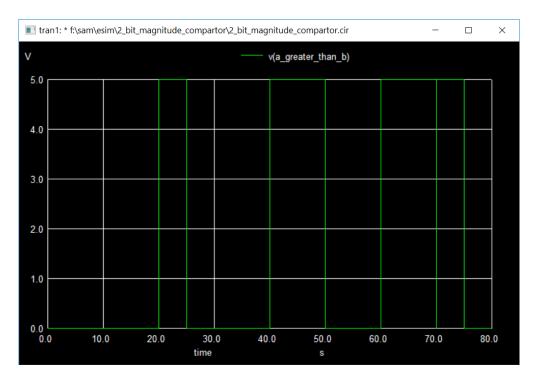

#### **OUTPUTS:**

A < B

A > B

• <u>PYTHON PLOTS:</u>

## INPUTS:

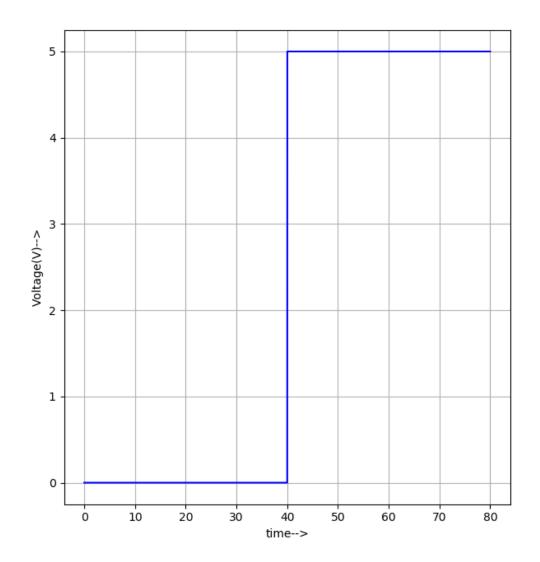

**A1**

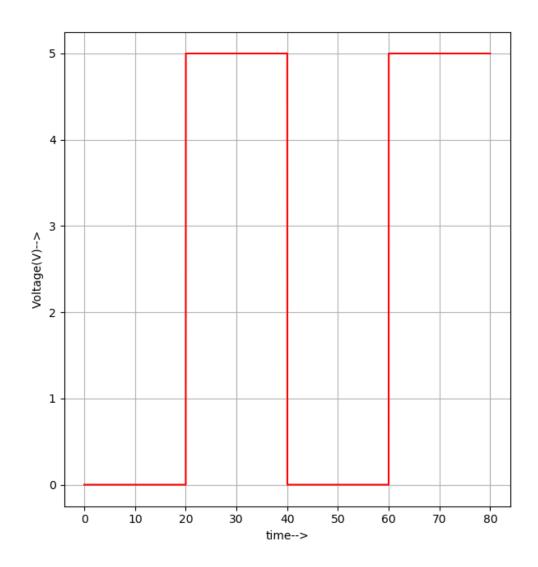

**A0**

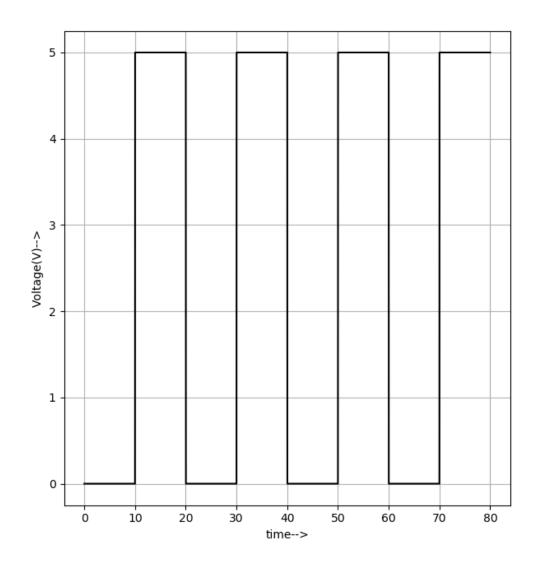

**B1**

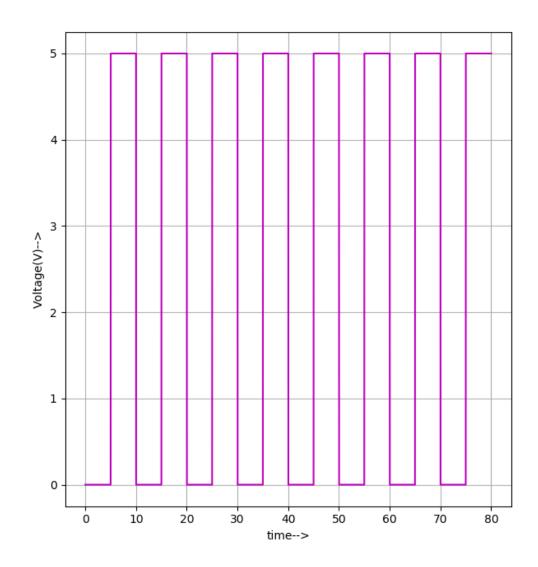

**B0**

### OUTPUTS:

A < B

A = B

A > B

### Source/Reference(s):

https://www.geeksforgeeks.org/magnitude-comparator-in-digital-logic/