# **Circuit Simulation Project**

https://esim.fossee.in/circuit-simulation-project

Name of the Participant: Dikshita Mehta (20BCE1056)

Project Guide: Dr R. Maheshwari

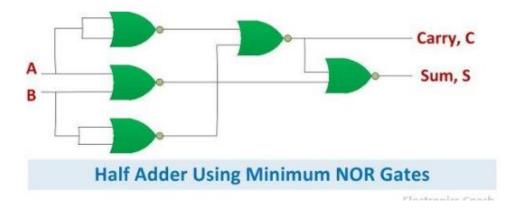

Title of the Circuit: Half Adder using NOR Gates

#### Description:

Half Adder is the digital circuit which can generate the result of the addition of two 1-bit numbers. It consists of two input terminals through which 1-bit numbers can be given for processing. After this, the half adder generates the sum of the numbers and carry if present.

The NOR gate is also a universal gate. Thus, it can also be used for designing of any digital circuit. The Half adder can be designed using 5 NOR gates. This is the minimum number of NOR gates to design half adder.

Firstly, three NOR gates are used in the designing and the output from two of these NOR gates is given to fourth NOR gate. The output from second NOR gate is given to the gate connected at the end. This will generate the sum bit of the addition of two 1-bit numbers.

# Circuit Diagram:

## Truth table:

| INPUTS |   | OUTPUTS |          |

|--------|---|---------|----------|

| А      | В | Sum(S)  | Carry(C) |

| 0      | 0 | 0       | 0        |

| 0      | 1 | 1       | 0        |

| 1      | o | 1       | 0        |

| 1      | 1 | 0       | 1        |

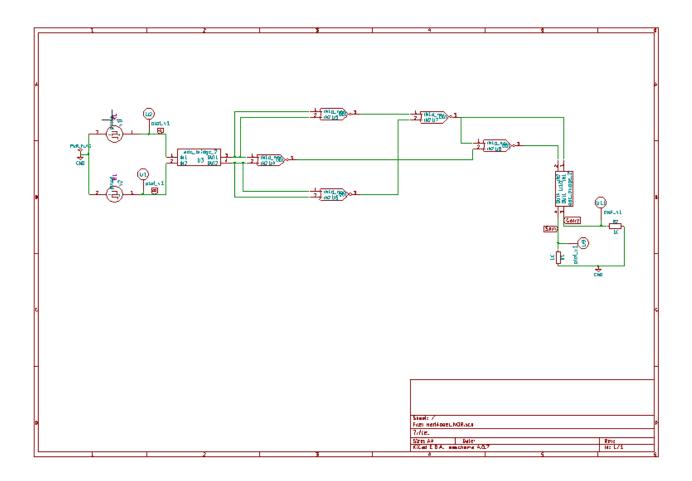

e-Sim Schematic:

Simulation Results:

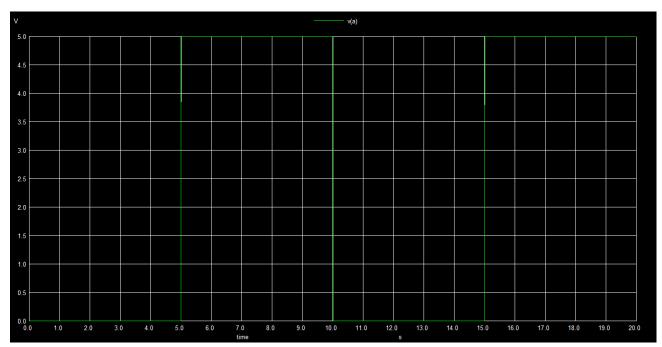

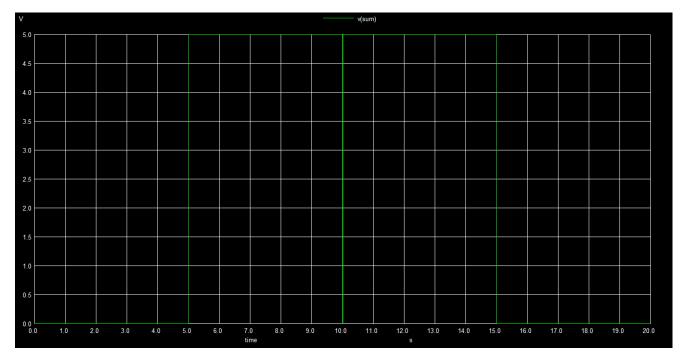

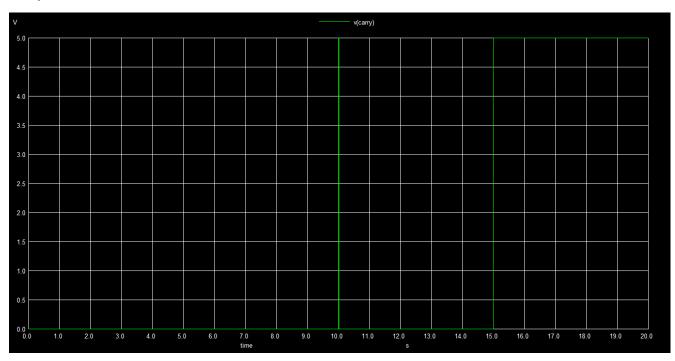

1. NgSpice Waveforms:

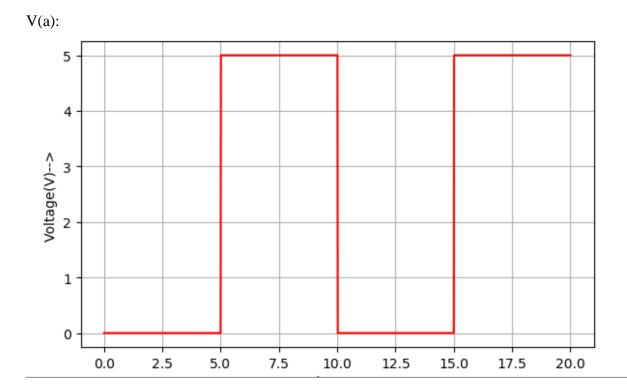

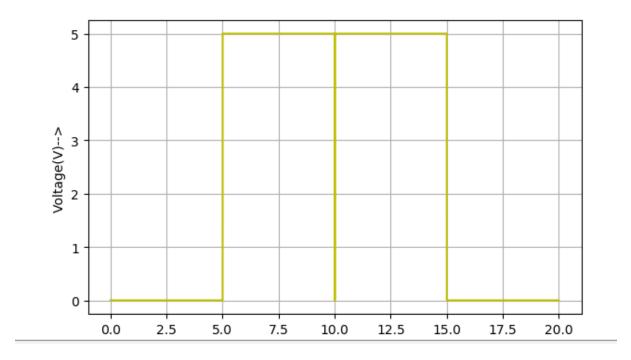

V(a):

### Sum:

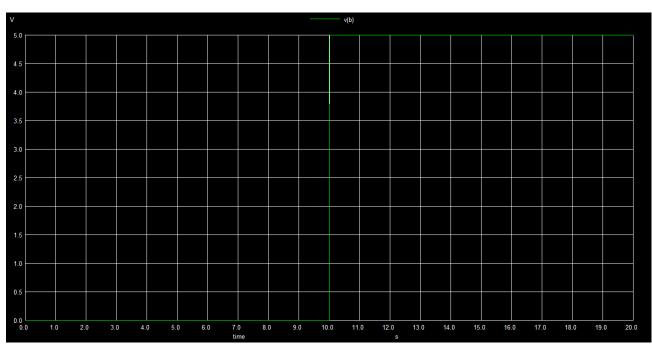

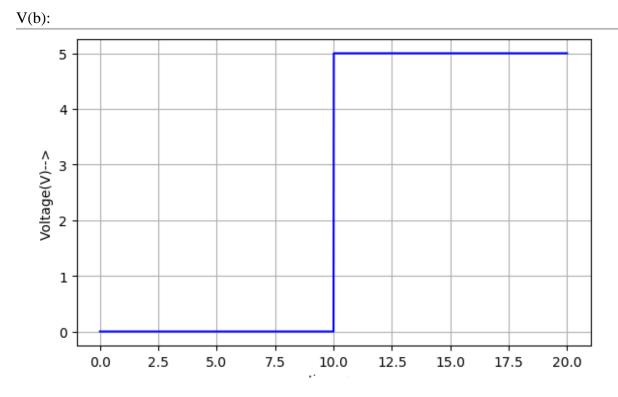

### V(b):

Carry:

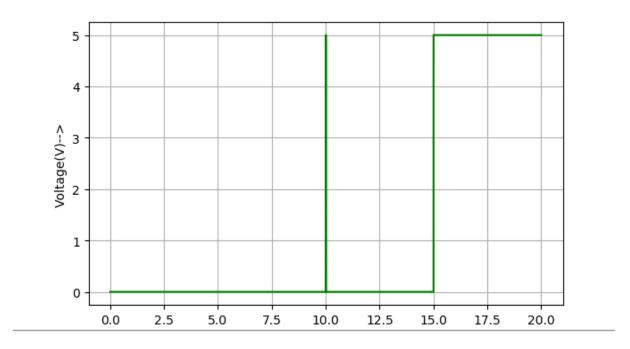

### 2. Python Waveforms:

Sum:

Carry:

#### Conclusion:

Thus, half adder was designed and the output plots were verified using esim.

References:

https://electronicscoach.com/half-adder.html