# <u>Circuit Simulation</u> <u>Project</u>

https://esim.fossee.in/circuitsimulation-project

Name of Participant: Abhimanyu Pundir

Project Guide: Dr. Maheshwari. R

Project Name: Design of full Adder using NOR gates

#### **Theory:-**

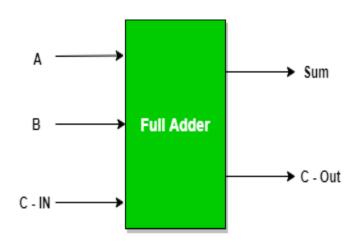

#### Full Adder:-

A full adder is a digital circuit that performs addition. Full adders are implemented with logic gates in hardware. A full adder adds three one-bit binary numbers, two operands and a carry bit. The adder outputs two numbers, a sum and a carry bit. The term is contrasted with a half adder, which adds two binary digits.

#### Full adder Truth Table:-

| Inputs |   |      | Outputs |       |

|--------|---|------|---------|-------|

| A      | В | C-IN | Sum     | C-Out |

| 0      | 0 | 0    | 0       | 0     |

| 0      | 0 | 1    | 1       | 0     |

| 0      | 1 | 0    | 1       | 0     |

| 0      | 1 | 1    | 0       | 1     |

| 1      | 0 | 0    | 1       | 0     |

| 1      | 0 | 1    | 0       | 1     |

| 1      | 1 | 0    | 0       | 1     |

| 1      | 1 | 1    | 1       | 1     |

### **NOR Gates:-**

The *NOR gate* is a combination OR gate followed by an inverter. Its output is "true" if both inputs are "false." Otherwise, the output is "false."

### **Truth table for NOR gate:-**

| Inputs |   | Outputs |  |

|--------|---|---------|--|

| Х      | Υ | Z       |  |

| 0      | 0 | 1       |  |

| 0      | 1 | 0       |  |

| 1      | 0 | 0       |  |

| 1      | 1 | 0       |  |

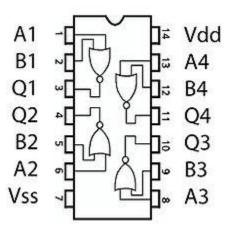

#### 4001 Quad NOR

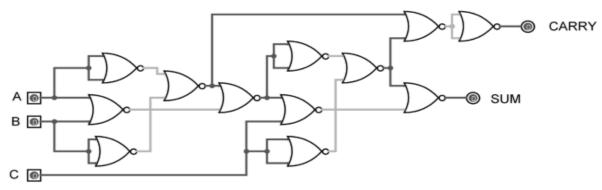

#### Schematic of full adder using NOR gate:-

#### **Logical Expression for SUM:**

- = A' B' C-IN + A' B C-IN' + A B' C-IN' + A B C-IN

- = C-IN (A' B' + A B) + C-IN' (A' B + A B')

- = C-IN XOR (A XOR B)

- =(1,2,4,7)

#### **Logical Expression for C-OUT:**

- = A' B C-IN + A B' C-IN + A B C-IN' + A B C-IN

- = A B + B C-IN + A C-IN

- =(3,5,6,7)

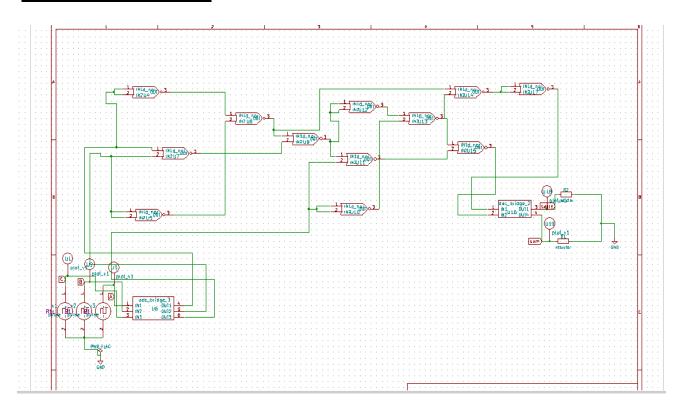

### **CIRCUIT DIAGRAM:**

### **OUTPUTS:-**

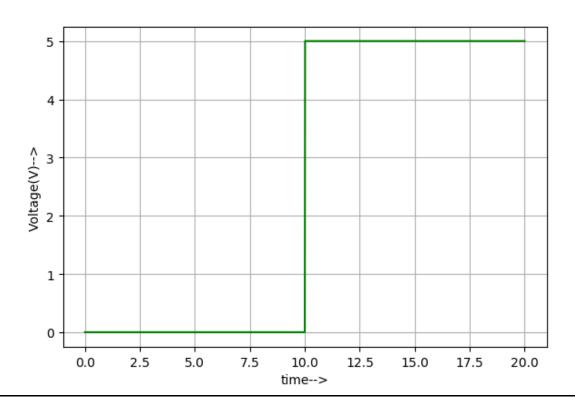

### **Python plots:-**

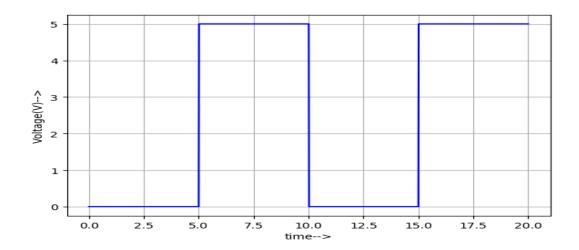

### Inputs:

Α

В

С

## Outputs:-

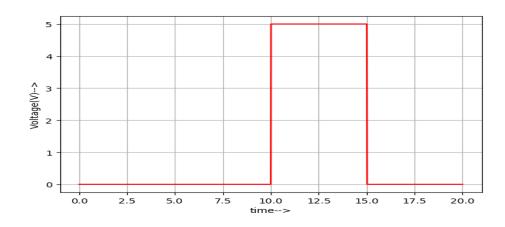

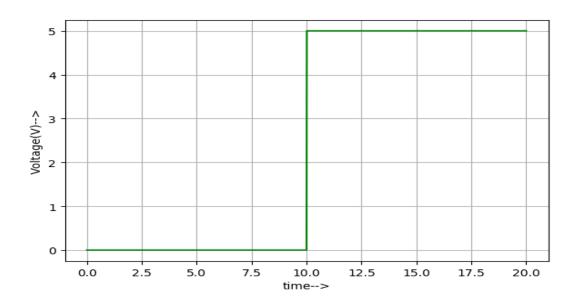

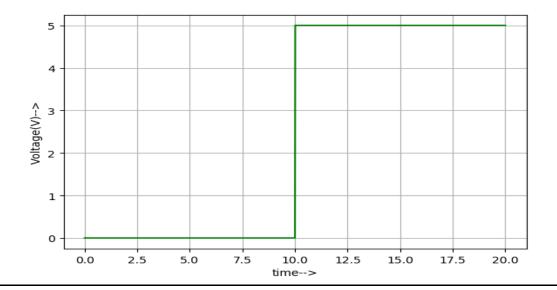

# SUM:-

# Carry:-

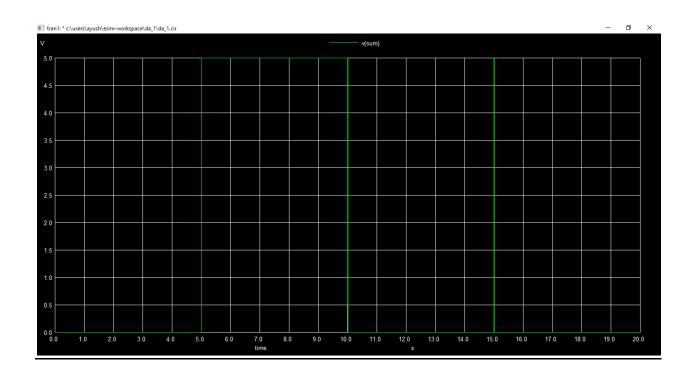

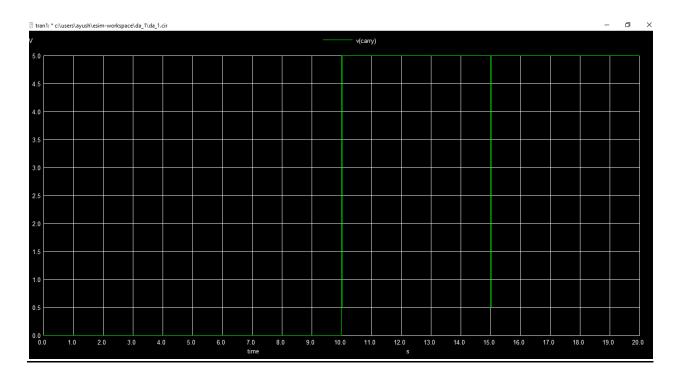

### **Ngspice Plots:-**

### Inputs:-

#### Α

### Outputs:-

### <u>Sum:-</u>

#### Carry:-

### **References:-**

- https://www.geeksforgeeks.org/full-adder-in-digital-logic/

- https://de-iitr.vlabs.ac.in/exp/half-full-adder/theory.html

- https://www.youtube.com/watch?v=9ymwX1Pzybk

- https://vimaxmedia.com/yv85f9/full-adder-using-nor-gate