**Circuit Simulation Project**

https://esim.fossee.in/circuit-simulation-project

| Name of the Participant - | Ms. Sai Samyuktha N |

|---------------------------|---------------------|

|                           |                     |

| Project Guide - | Dr. Maheswari.R |

|-----------------|-----------------|

|-----------------|-----------------|

Title of the Project -Design of a 4-bit Gray to Binary code converter circuitwith Main circuit and Subciruit implementation using<br/>eSim

### **Theory**

- *Binary* Binary code is based on a binary number system in which there are only two possible states, off and on, usually symbolized by 0 and 1.

- *Gray code* Gray code is an ordering of the binary numeral system such that two successive values differ in only one bit.

- Decimal Gray Code Binary

- The following table is a comparison of Decimal, Gray code and Binary:

Image source : <u>https://www.dynapar.com/hs-fs/hubfs/uploadedImages/\_Site\_Root/Gray-</u> Code-Encoder-Output.jpg?width=219&height=319&name=Gray-Code-Encoder-Output.jpg

### • Gray to Binary code conversion:

The truth table of Gray to Binary code conversion is:

Gray code number is the input and the corresponding Binary form is the Output. Decimal number is taken for reference (in the table)

| Decimal        |   | INF | PUT |   |   | OUT | TPUT | U <b>T</b> |  |

|----------------|---|-----|-----|---|---|-----|------|------------|--|

| Number<br>rep. | Α | В   | С   | D | W | X   | Y    | Z          |  |

| 0              | 0 | 0   | 0   | 0 | 0 | 0   | 0    | 0          |  |

| 1              | 0 | 0   | 0   | 1 | 0 | 0   | 0    | 1          |  |

| 2              | 0 | 0   | 1   | 0 | 0 | 0   | 1    | 1          |  |

| 3              | 0 | 0   | 1   | 1 | 0 | 0   | 1    | 0          |  |

| 4              | 0 | 1   | 0   | 0 | 0 | 1   | 1    | 1          |  |

| 5              | 0 | 1   | 0   | 1 | 0 | 1   | 1    | 0          |  |

| 6              | 0 | 1   | 1   | 0 | 0 | 1   | 0    | 0          |  |

| 7              | 0 | 1   | 1   | 1 | 0 | 1   | 0    | 1          |  |

| 8              | 1 | 0   | 0   | 0 | 1 | 1   | 1    | 1          |  |

| 9              | 1 | 0   | 0   | 1 | 1 | 1   | 1    | 0          |  |

| 10             | 1 | 0   | 1   | 0 | 1 | 1   | 0    | 0          |  |

| 11             | 1 | 0   | 1   | 1 | 1 | 1   | 0    | 1          |  |

| 12             | 1 | 1   | 0   | 0 | 1 | 0   | 0    | 0          |  |

| 13             | 1 | 1   | 0   | 1 | 1 | 0   | 0    | 1          |  |

| 14             | 1 | 1   | 1   | 0 | 1 | 0   | 1    | 1          |  |

| 15             | 1 | 1   | 1   | 1 | 1 | 0   | 1    | 0          |  |

### Truth Table reduction using K-Map:

1) W

| C D<br>A B | 00 | 01 | 11 | 10 |

|------------|----|----|----|----|

| 00         | 0  | 0  | 0  | 0  |

| 01         | 0  | 0  | 0  | 0  |

| 11         | 1  | 1  | 1  | 1  |

| 10         | 1  | 1  | 1  | 1  |

Hence,

$$W = A$$

2) X

| C D<br>A B | 00 | 01 | 11 | 10 |

|------------|----|----|----|----|

| 00         | 0  | 0  | 0  | 0  |

| 01         | 1  | 1  | 1  | 1  |

| 11         | 0  | 0  | 0  | 0  |

| 10         | 1  | 1  | 1  | 1  |

$$X = (A'.B) + (A.B')$$

Hence,

$$X = A \oplus B$$

3) Y

| C D | 00 | 01 | 11 | 10 |

|-----|----|----|----|----|

| 00  | 0  | 0  | 1  | 1  |

| 01  | 1  | 1  | 0  | 0  |

| 11  | 0  | 0  | 1  | 1  |

| 10  | 1  | 1  | 0  | 0  |

Y = (A'.B'.C) + (A'.B.C') + (A.B.C) + (A.B'.C')Hence, on simplification  $Y = X \bigoplus C$

4) Z

| C D | 00 | 01 | 11 | 10 |

|-----|----|----|----|----|

| 00  | 0  | 1  | 0  | 1  |

| 01  | 1  | 0  | 1  | 0  |

| 11  | 0  | 1  | 0  | 1  |

| 10  | 1  | 0  | 1  | 0  |

Z = (A'.B'.C'.D) + (A'.B'.C.D') + (A'.B.C'.D') + (A'.B.C.D) + (A.B.C'.D) + (A.B.C'.D) + (A.B.C.D) + (A.B.C.D') + (A.B'.C'.D') + (A.B'.C.D)Hence, on simplification,  $Z = Y \bigoplus D$

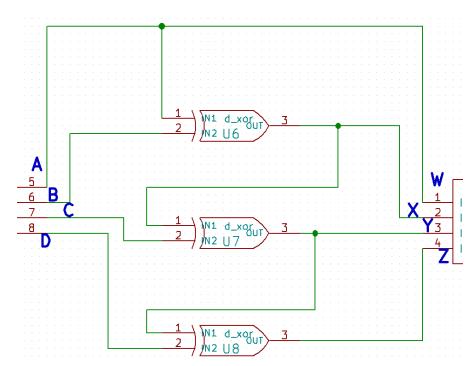

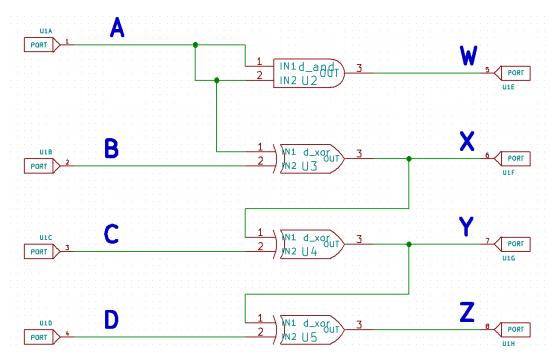

### • Circuit Diagram:

The circuit can be implemented using three x-or gates

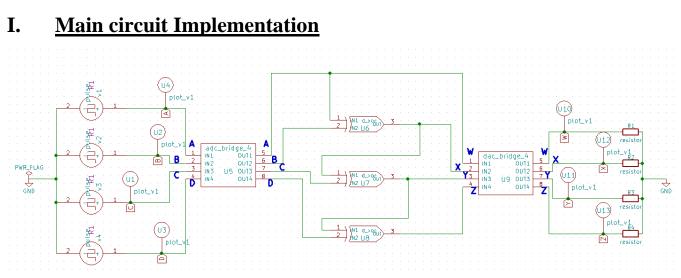

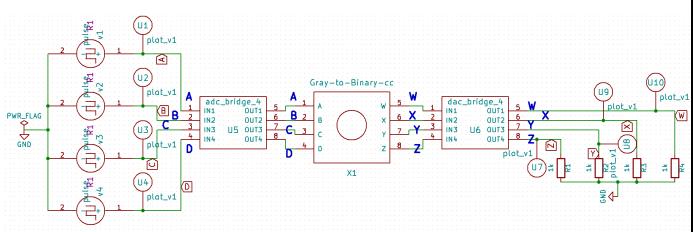

### eSim Implementation

The main circuit has three parts:

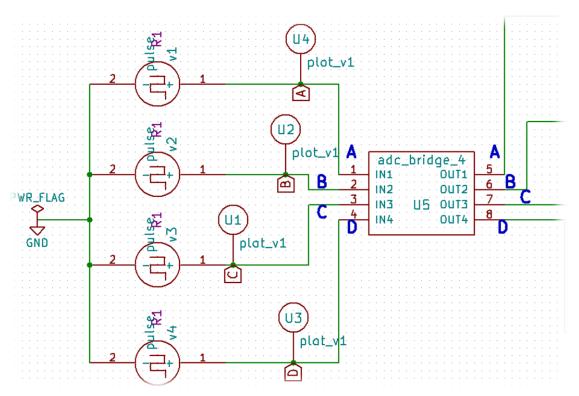

### 1. Input

The 4-bit Gray code input is of the form :- A B C D

We make use of the analog to digital converter to convert the input analog pulses into digital as we make use of logic gates (that work only on digital signals)

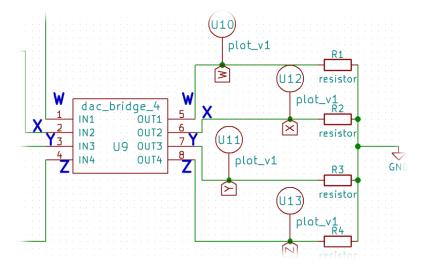

### 2. Output

The 4-bit Binary output is of the form :- W X Y Z

We make use of the digital to analog converter to convert the signals back into analog and compute the output

### 3. Logic Circuit

The circuit has been implemented from the previously derived logic circuit diagram.

# Kicad to Ngspice Conversion

Here we make use of transient analysis:

| nalysis Source Details Ngs | pice Model Device Modeling Sul | circuits  |   |

|----------------------------|--------------------------------|-----------|---|

| Select Analysis Type       |                                |           |   |

| AC                         | DC                             | TRANSIENT |   |

| Transient Analysis         |                                |           |   |

| Start Time                 |                                | 0 Sec     | ~ |

| Step Time                  |                                | 5 ms      | ~ |

| Stop Time                  |                                | 80 Sec    | ~ |

| Stop Time                  |                                | 80 Sec    | ~ |

### Source Details:

| Analysis   | Source Details        | Ngspice Model Device Modeling Subcircuits |    |  |  |  |

|------------|-----------------------|-------------------------------------------|----|--|--|--|

| - Add para | ameters for pulse so  | urce v1                                   |    |  |  |  |

| Enter ir   | nitial value(Volts/Ar | nps):                                     | 0  |  |  |  |

| Enter p    | ulsed value(Volts/A   | mps):                                     | 5  |  |  |  |

| Enter d    | lelay time (seconds)  | :                                         | 40 |  |  |  |

| Enter ri   | ise time (seconds):   |                                           | 0  |  |  |  |

| Enter fa   | all time (seconds):   |                                           | 0  |  |  |  |

| Enter p    | ulse width (seconds   | ):                                        | 40 |  |  |  |

| Enter p    | eriod (seconds):      |                                           | 80 |  |  |  |

| - Add para | ameters for pulse so  | urce v2                                   |    |  |  |  |

| Enter ir   | nitial value(Volts/Ar | nps):                                     | 0  |  |  |  |

| Enter p    | ulsed value(Volts/A   | mps):                                     | 5  |  |  |  |

| Enter d    | lelay time (seconds)  |                                           | 20 |  |  |  |

| Enter ri   | ise time (seconds):   |                                           | 0  |  |  |  |

| Enter fa   | all time (seconds):   |                                           | 0  |  |  |  |

| Enter p    | ulse width (seconds   | ):                                        | 20 |  |  |  |

| Enter p    | eriod (seconds):      |                                           | 40 |  |  |  |

| Analysis  | Source Details         | Ngspice Model Device Modeling Subcircuits |    |

|-----------|------------------------|-------------------------------------------|----|

| - Add par | rameters for pulse s   | ource v3                                  | ^  |

| Enter i   | initial value(Volts/Ar | nps):                                     | 0  |

| Enter p   | pulsed value(Volts/#   | imps):                                    | 5  |

| Enter o   | delay time (seconds    | ):                                        | 10 |

| Enter r   | rise time (seconds):   |                                           | 0  |

| Enter f   | fall time (seconds):   |                                           | 0  |

| Enter p   | pulse width (second    | 5):                                       | 10 |

| Enter p   | period (seconds):      |                                           | 20 |

| Add par   | rameters for pulse s   | purce v4                                  |    |

| Enter i   | initial value(Volts/A  | nps):                                     | 0  |

| Enter p   | pulsed value(Volts/#   | imps):                                    | 5  |

| Enter o   | delay time (seconds    | :                                         | 5  |

| Enter r   | rise time (seconds):   |                                           | 0  |

| Enter f   | fall time (seconds):   |                                           | 0  |

| Enter p   | pulse width (second    | 5):                                       | 5  |

| Enter p   | period (seconds):      |                                           | 10 |

Other fields are left as default.

## **<u>Circuit simulation Output</u>**

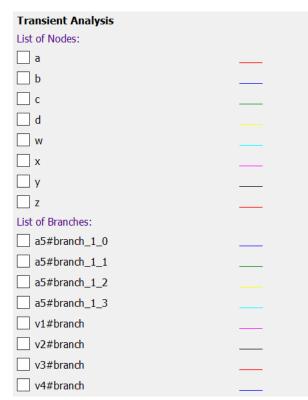

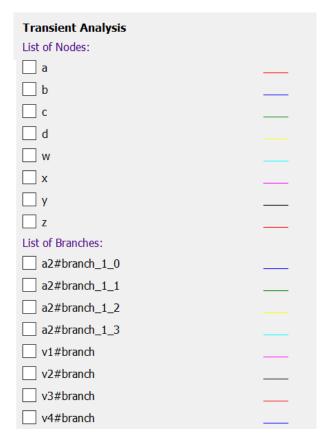

### I. <u>NGSPICE PLOTS:</u>

#### • Inputs:

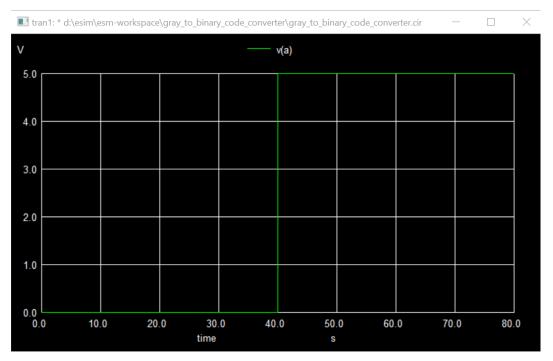

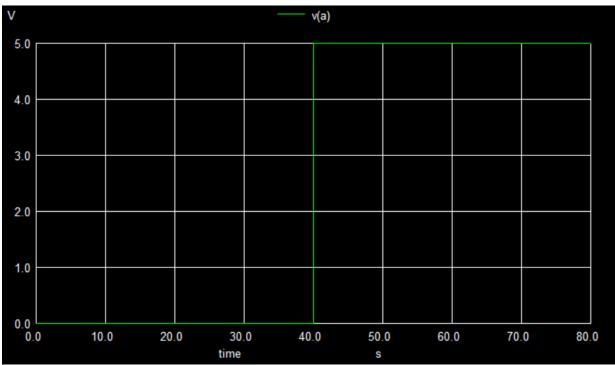

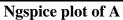

### Ngspice plot of A

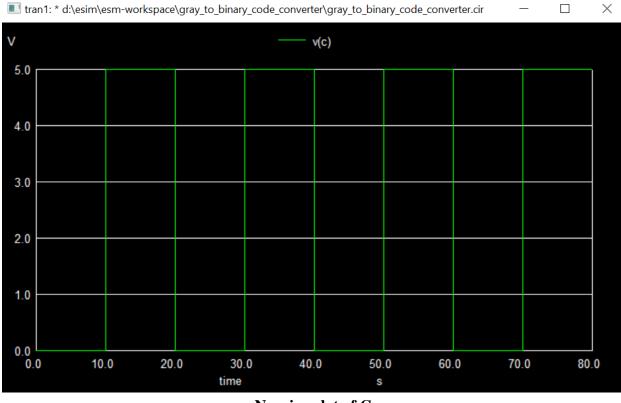

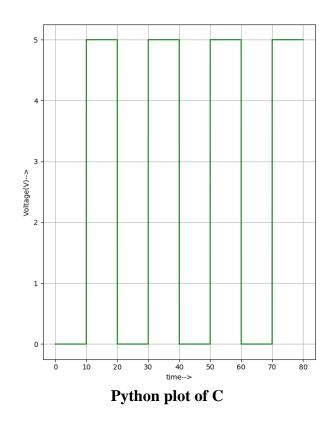

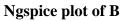

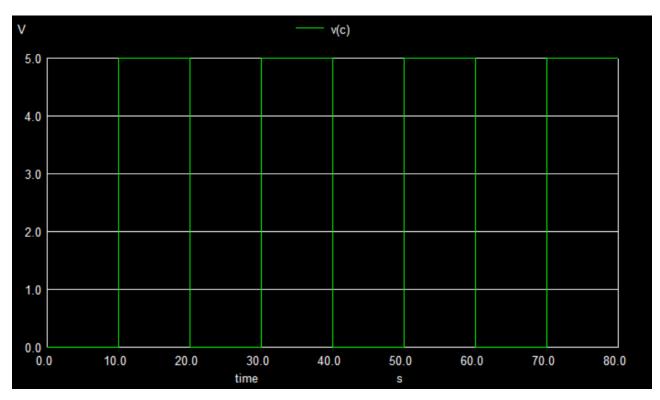

Ngspice plot of C

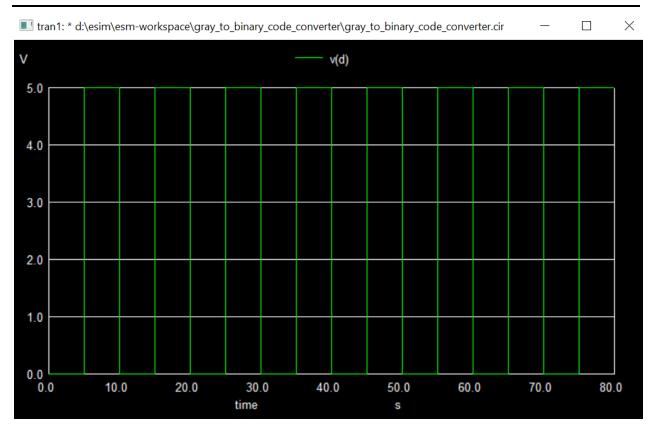

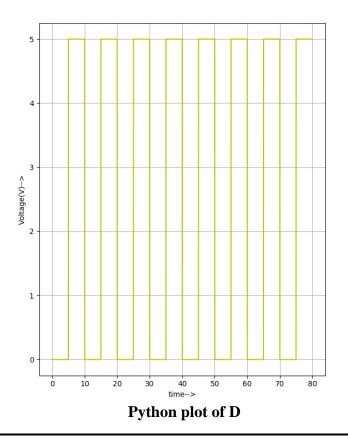

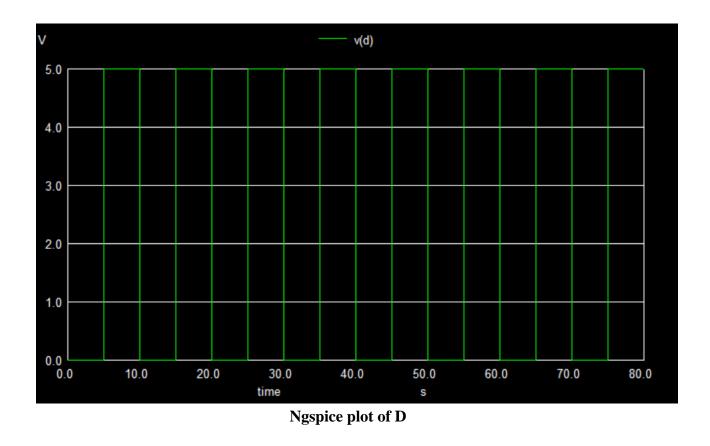

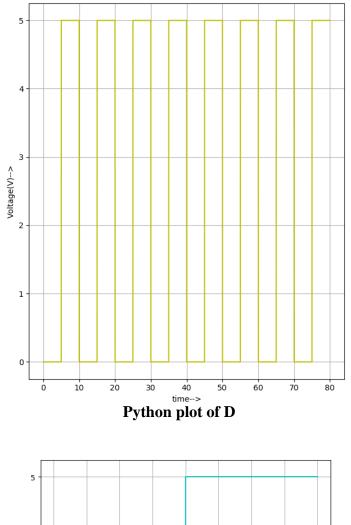

Ngspice plot of D

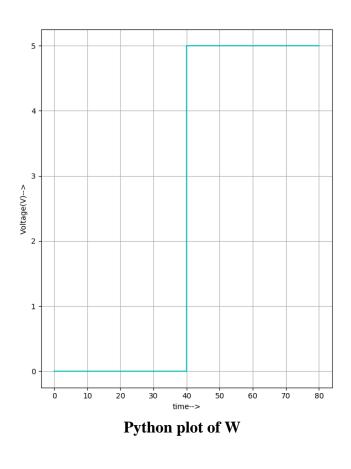

#### • Outputs:

🔳 tran1: \* d:\esim\esm-workspace\gray\_to\_binary\_code\_converter\gray\_to\_binary\_code\_converter.cir – 🛛 🛛 🗡

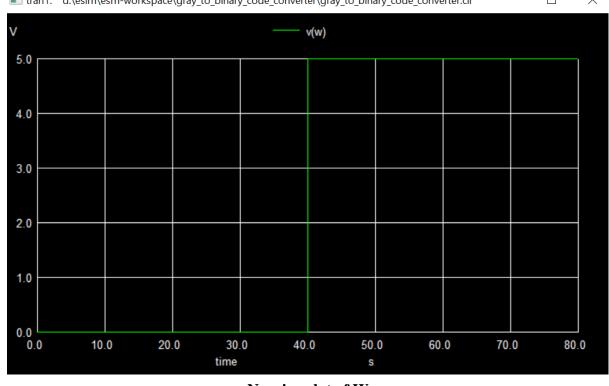

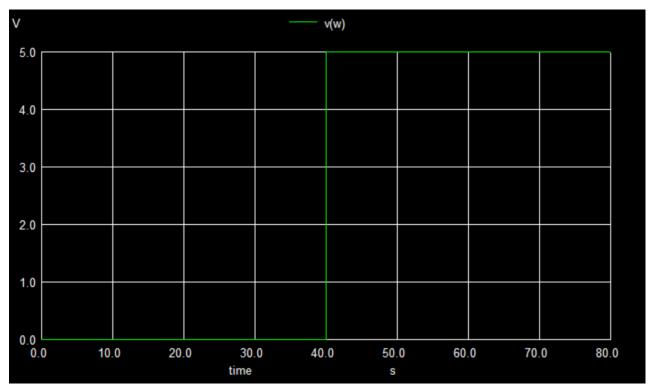

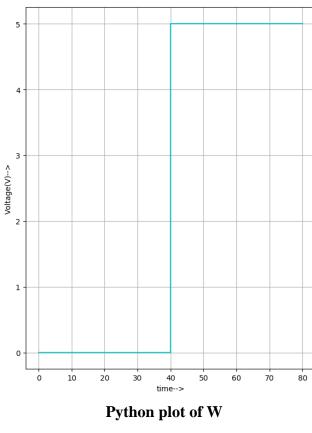

#### Ngspice plot of W

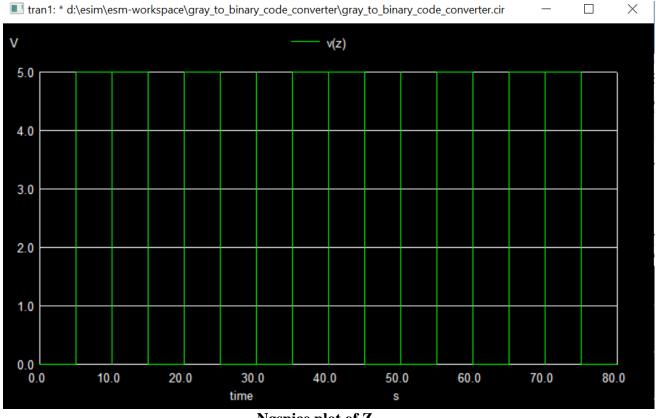

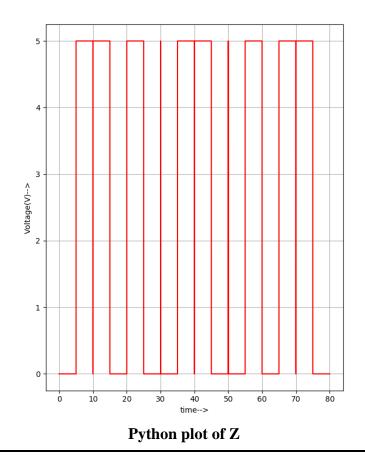

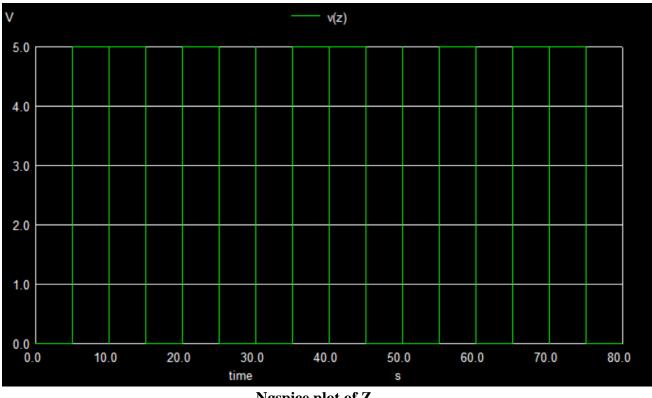

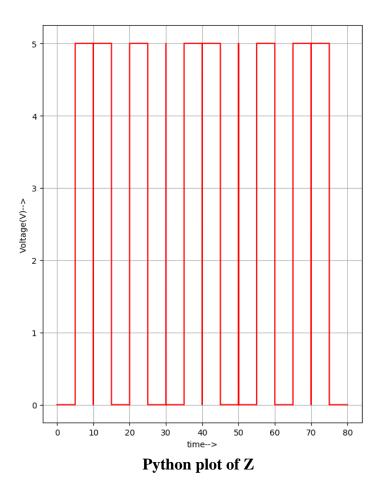

Ngspice plot of Z

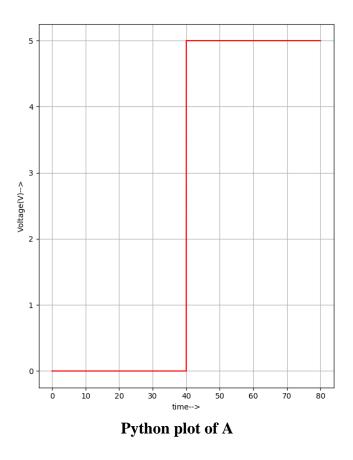

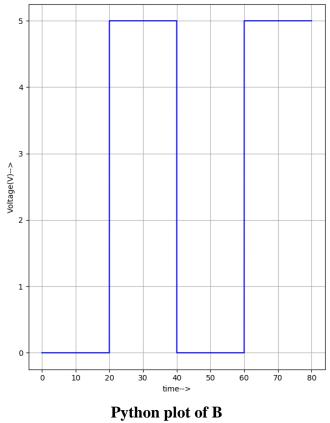

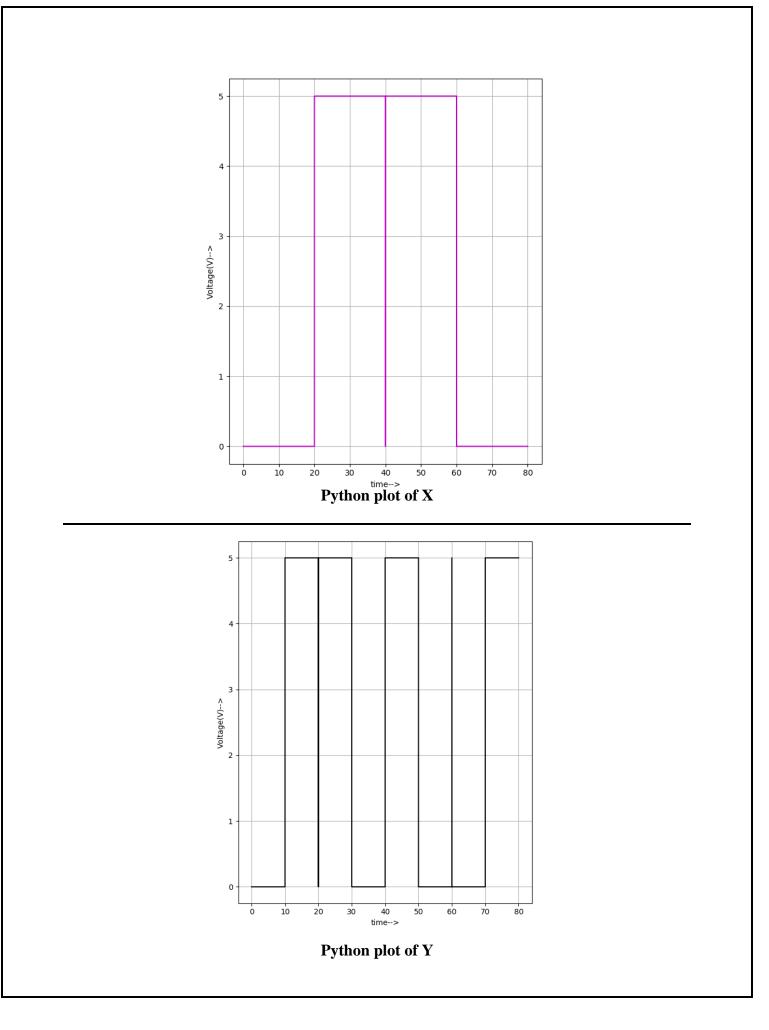

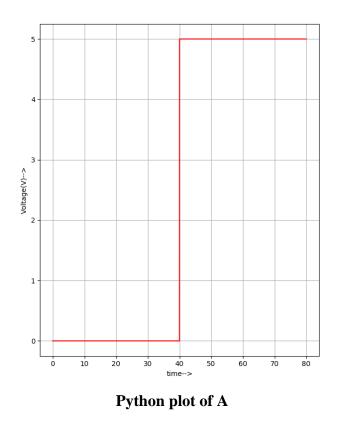

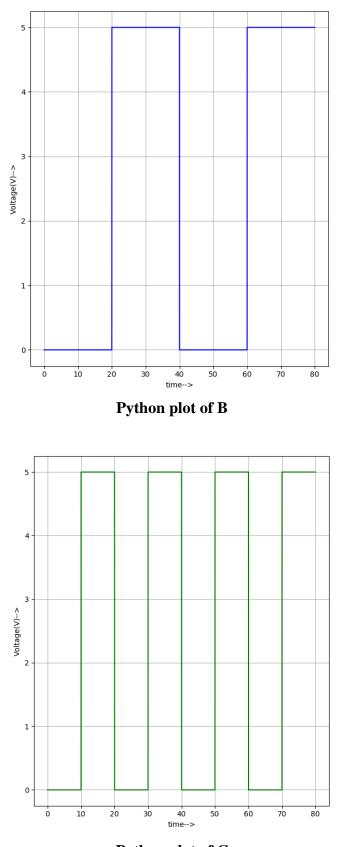

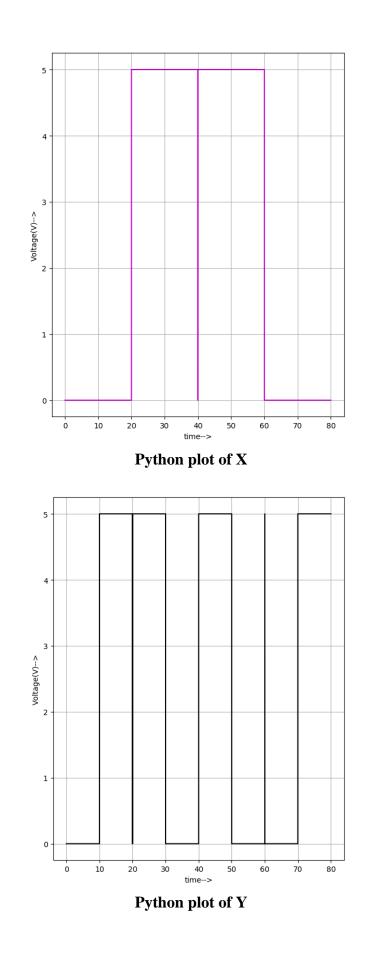

### II. <u>PYTHON PLOTS:</u>

• Inputs:

• Outputs:

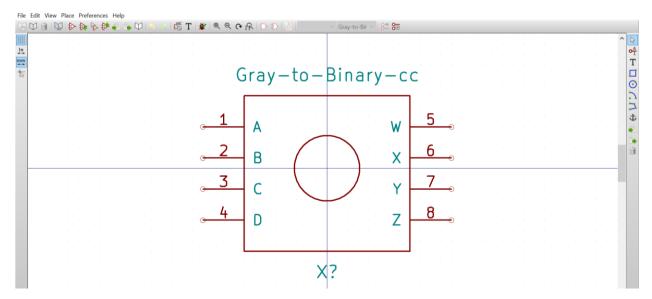

### II. Sub circuit Implementation

#### **Creating the Subcircuit:**

Here, we make use of an additional AND gate for sub-circuit implementation. When both the inputs of the AND gate is A, it gives the same (A) as the output. Hence, it does not affect the functionality of the circuit.

#### <u>Creating the circuit symbol using Library editor :</u>

- Create new component -> Enter component name and Default reference designator (X since user defined)

- **U**raw the symbol, Generate netlist and save it (under eSim\_Subckt library)

### Create new project - new schematic:

Schematic design using subcircuit

### Kicad to Ngspice Conversion:

We use the same transient analysis parameters as the main circuit, but in addition, we mention the path of the sub circuit used:

| oNgspice- | 2                     |                    |                               |                 |      |      |      |

|-----------|-----------------------|--------------------|-------------------------------|-----------------|------|------|------|

| Analysis  | Source Details        | Ngspice Model      | Device Modeling               | Subcircuits     |      |      |      |

| Add subo  | circuit for gray-to-b | inary-cc           |                               |                 | <br> | <br> |      |

|           |                       |                    |                               |                 |      |      |      |

|           |                       |                    |                               |                 |      |      |      |

| D:\ESim   | \Installation files\F | OSSEE\eSim\librarv | \SubcircuitLibrary\Gravestics | av to Binarv cc |      |      | Add  |

|           | <u> </u>              |                    |                               |                 |      |      |      |

|           |                       |                    |                               |                 |      |      |      |

|           |                       |                    |                               |                 |      |      |      |

|           |                       |                    |                               |                 |      |      |      |

|           |                       |                    |                               |                 |      |      | Conv |

### **<u>Circuit simulation Output</u>**

#### I. **Ngspice Plots**

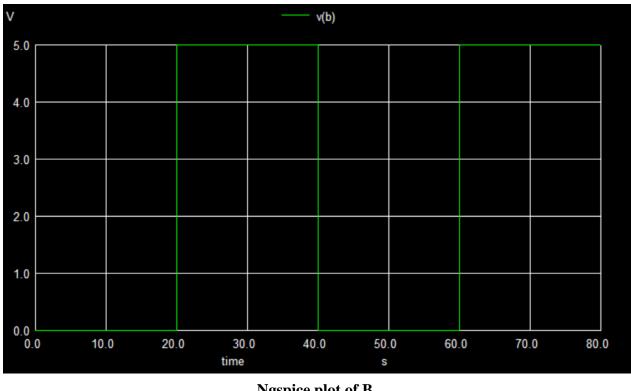

### Inputs:

Ngspice plot of C

### Outputs:

### Ngspice plot of W

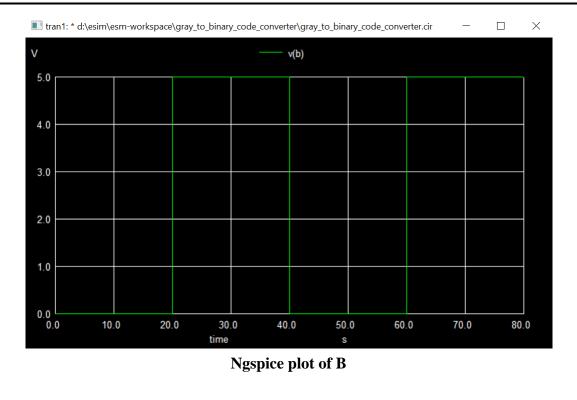

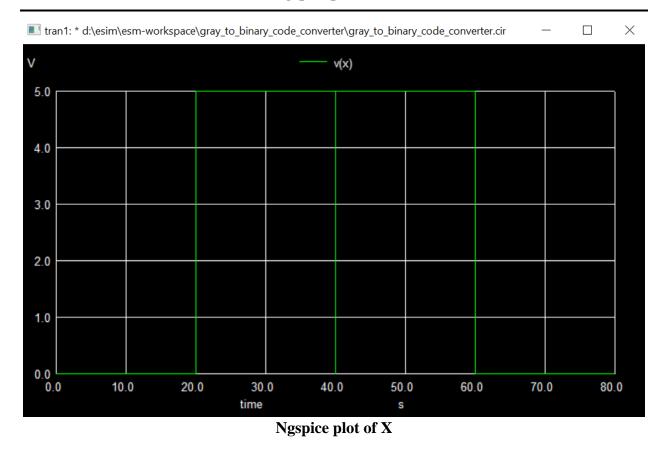

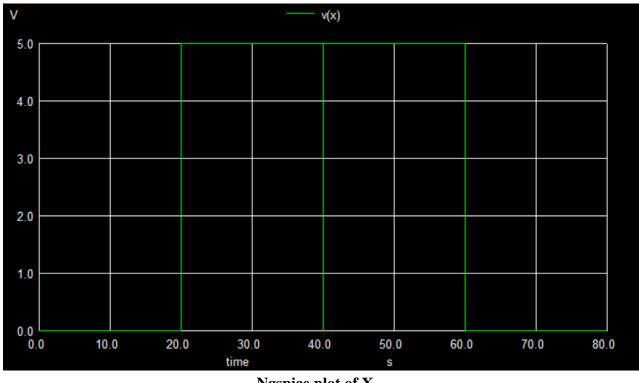

Ngspice plot of X

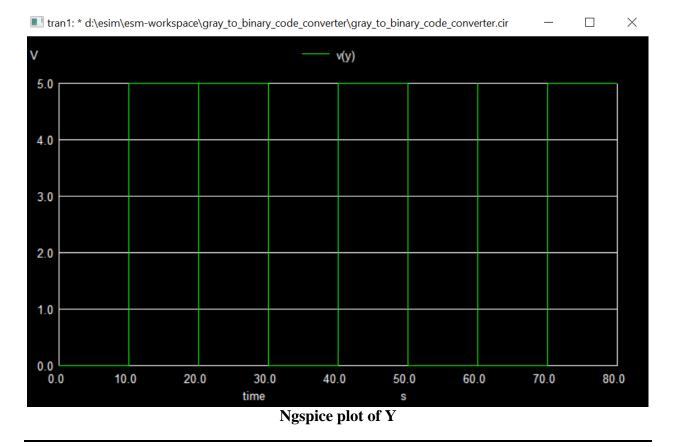

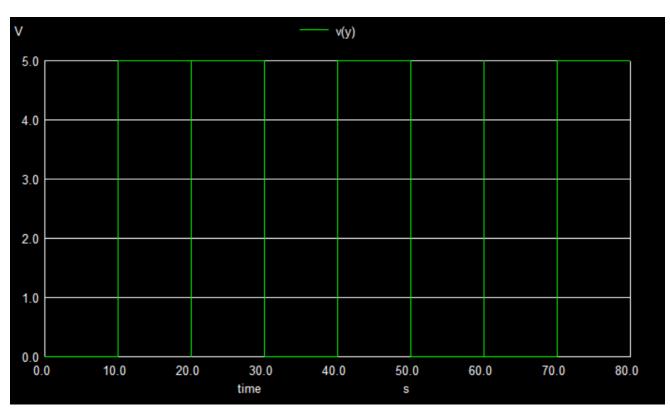

Ngspice plot of Y

Ngspice plot of Z

### **II.** Python Plots

### Inputs:

Python plot of C

### **Result:**

Both the circuits give the same output. Thus, a Gray to Binary code converter has been created along with Main circuit and Subcircuit implementation. The outputs have also been verified.

### **References:**

https://electricalworkbook.com/design-of-binary-to-gray-code-converter-circuit/