# **Circuit Simulation Project**

https://esim.fossee.in/circuit-simulation-project

Name of the participant: Hrushikesh Kulkarni

Project guide: Neethi M

Title of the circuit: Three Phase Halfwave Uncontrolled Rectifier with RL Load

#### Theory/Description:

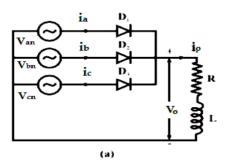

As many loads usually need a dc input for operation and the supply usually comes as 3 phase AC, 3 phase rectification is preferred. Fig-a usually known as "maximum value" circuit has 3 diodes whose anodes are connected to each phase of supply and cathode are connected to common terminal to form positive load terminal.

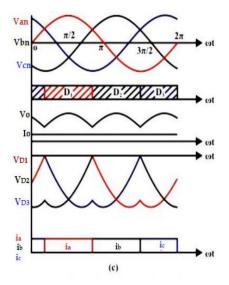

As the diode block the negative voltages, thus they conduct only when that phase voltage is maximum of three. Conduction table Fig-b indicates the conduction and appearance of voltages according to which waveforms of Fig-c are easily obtained from the circuit.

| Voltages<br>Mode | V <sub>D1</sub> | $V_{D2}$ | V <sub>D3</sub> | Vo       |

|------------------|-----------------|----------|-----------------|----------|

| D1               | 0               | $V_{ba}$ | $V_{ca}$        | $V_{an}$ |

| D2               | $V_{ab}$        | 0        | $V_{cb}$        | $V_{bn}$ |

| D3               | V <sub>ac</sub> | $V_{bc}$ | 0               | $V_{cn}$ |

|                  | (b)             |          |                 |          |

Note that the load current( $I_0$ ) is taken to be ripple free.

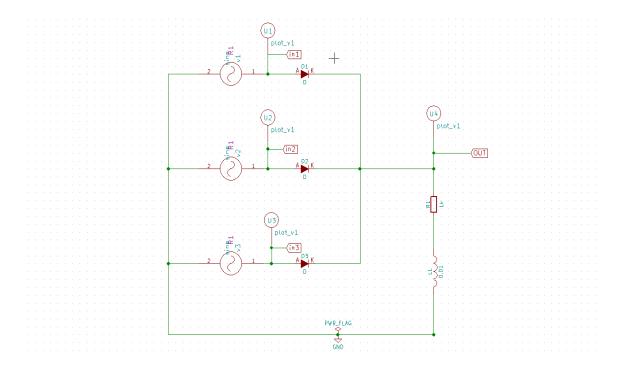

## Circuit Diagram(s):

#### Results (Input, Output waveforms and/or Multimeter readings):

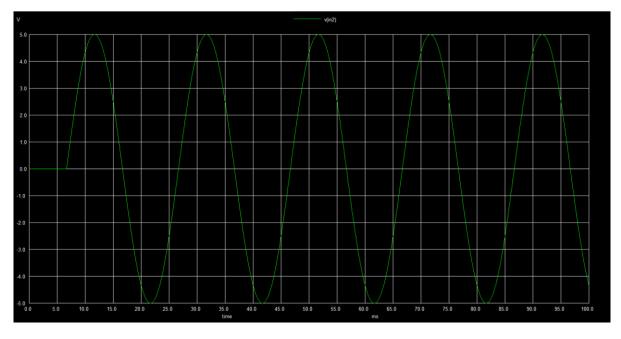

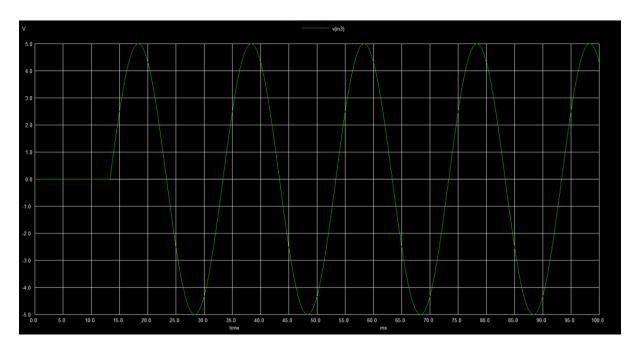

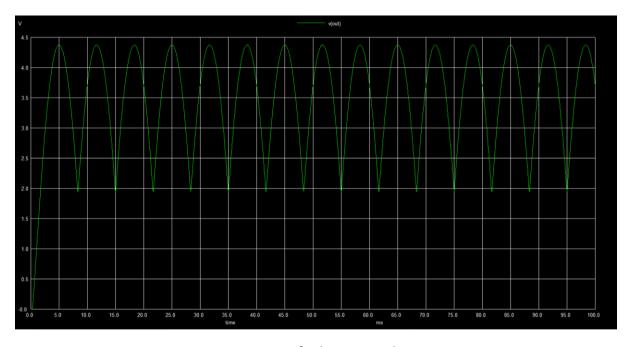

#### 1. Ng-Spice:

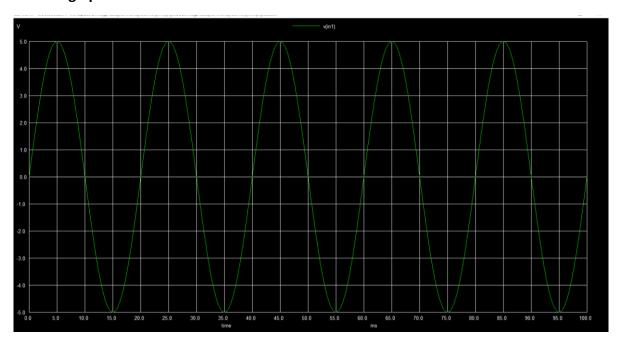

Figure1: Input voltage waveform with zero delay time

Figure 2: Input voltage with 0.00667 delay time

Figure3: Input voltage with 0.01333 delay time

Figure4: Rectified output voltage

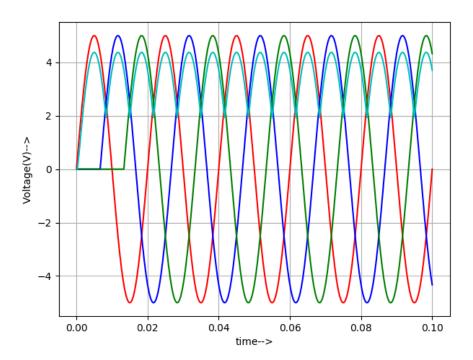

## **Python Plot:**

Figure 5: Three phase input and Rectified output

### Source/Reference(s):

$1.\ https://ceng.tu.edu.iq/eed/images/PE\_lect7.compressed.pdf$