# **Circuit Simulation Project**

https://esim.fossee.in/circuit-simulation-project

# 6-Bit Unsigned Multiplier Circuit With Dadda Tree Reduction And Brent-Kung Adder

Ву

#### Reuel Reuben

Under the Guidance of Prof. A. Prabhakar and Prof. Swapnil S. Thorat

# Theory/Description:

Adders and Multipliers are integral part of any modern day SOC/Processor. They are usually a part of the arithmetic unit, or ALU. The ALU can be found at the core of every digital computer and are one of the most important parts of a CPU.

Since we need more and more performance for up-to-date applications there is a need to increase the speed as well as the performance and reduce the delay of these Adders and Multipliers. This kind of performance boost and delay reduction can be seen in the Parallel Multipliers such as the Dadda Tree Multiplier and the Parallel Prefix Adders such as the Brent Kung Adder.

#### **Dadda Tree Reduction Multiplier:**

This Multiplier is very similar to the Wallace tree Multiplier but this multiplier has some key advantages over the Wallace tree Multiplier such as using lesser number of gates and decreasing the overall delay of the multiplier by the Dadda reduction technique.

The Dadda reduction technique is based on the Wallace Tree Reduction table which gives us the information of number of levels present in the Wallace reduction tree based on the number of partial products.

# NUMBER OF LEVELS IN WALLACE TREE

| Number of<br>Partial<br>Products,(k) | Number of Levels<br>in the Wallace Tree |  |  |  |  |

|--------------------------------------|-----------------------------------------|--|--|--|--|

| 3                                    | 1                                       |  |  |  |  |

| 4                                    | 2                                       |  |  |  |  |

| $5 \le k \le 6$                      | 3                                       |  |  |  |  |

| $7 \le k \le 9$                      | 4                                       |  |  |  |  |

| $10 \le k \le 13$                    | 5                                       |  |  |  |  |

| $14 \leq k \leq 19$                  | 6                                       |  |  |  |  |

| $20 \leq k \leq 28$                  | 7                                       |  |  |  |  |

| $29 \le k \le 42$                    | 8                                       |  |  |  |  |

| $43 \le k \le 63$                    | 9                                       |  |  |  |  |

From the table we know the number of levels we have to reduce in order to reach just 2 partial products. Since we are designing a 6x6 Dadda Tree Multiplier we can conclude that we need to reduce 3 levels in order to reach 2 partial products.

|            |          |       | 1          |           |      |     |    |                    |

|------------|----------|-------|------------|-----------|------|-----|----|--------------------|

|            |          |       | 6 15       | 1h        | 13   | 12  | 11 | -                  |

| *          |          | 26    | 28 24      | 2.5       | 22   | 21  |    | 6 PARTIAL          |

|            | 3.6      | 25    | 34 39      | 32        | 31   |     |    | PRODUCTS           |

| h.t        | 45       | h     | 15 12      | 3,        |      |     |    | 3 LEVEL            |

| S. S.      | 5,6      | 53    | 57 21      |           |      | 1   |    |                    |

| 66 65 61   | 63       | 62    | 6.         | ·         |      |     |    |                    |

| •          | c16 -c19 | *e15  | . C11      |           |      |     | w. |                    |

|            | . ciz    | 0013. | 8          |           |      |     |    | 18                 |

| . C6 26 M  |          | 0     |            | 11/1      | 13   | ;2  | ** | ,                  |

| 65 55      |          | .     | 0 22       | 2.3<br>6. | 22   | 21  |    | 4 PARTIAL PRODUCTS |

| e,         |          |       | 38         |           | 31   |     |    | 2 LEVEL            |

| e.H        |          | -     | 11 311     | 1/2       |      |     |    | 2 L F V C =        |

| 6 26 c2    |          |       | 22 621     |           |      |     |    |                    |

| 66 30 52   | 525      |       | 23   54"   | 23        | 1,2  | 12  | 61 | 3 PARTIAL          |

| 65 cl      | 11 . 1   |       | en sn      |           | 22   | 2.1 | į  | PRODUCTS           |

| e16 e1     |          |       | E 22   C21 | SZI       | 31   | 3 ' | -1 | 1 LEVEL            |

| cit cit ci |          |       | 33 C3r     | C31       |      | - 1 |    |                    |

| 66 518 53  |          | -     | 3 3 h 533  | 534       | 5,31 | 147 | 11 | 2 PARTIAL          |

| e38 e37 e3 | 16 - 638 | e34   | :33 :32    | 231       | 13   | Ť,  |    | PRODUCT            |

|            | 55       |       | 7          |           |      |     |    |                    |

|            | •        | - 34  |            | ,         | de . | *   | 1  | ×                  |

|            | •        |       | •          |           |      |     |    |                    |

|            | •        |       | HALF       | . 1       |      |     |    |                    |

|            | FULL     |       | ADDE       | R         |      |     |    | 9                  |

|            | Ann      | ER    |            |           |      |     |    |                    |

As seen above we can reduce the 6 partial products to 2 partial products. Once we reach 2 partial products, we can easily add both the partial product to get our multipliers result. In this project I have used a Brent Kung Adder to add the two partial products in order to get our result.

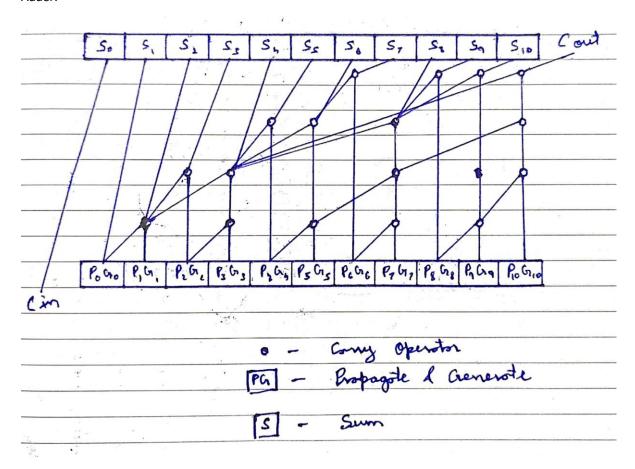

#### **Brent Kung Adder:**

Brent Kung adder is a parallel prefix adder. Some of the advantages of the Brent Kung adder is that it introduces higher consistency to the adder structure, it has lesser wiring cramming and lesser chip area to implement compared to the Kogge Stone adder.

Since the output of the Dadda Tree Multiplier is 2 11-bit partial products we need to make a 11-bit Brent Kung Adder.

For the brent kung we use the Generate and Propagate logic to make the parallel prefix adder

First we create the generate and propagate for all the inputs using formula

$$G(i) = Xi * Yi$$

$$P(i) = Xi$$

$\bigcirc$   $\bigcirc$   $\bigcirc$  Yi

$$C(i+1) = G(i) + P(i) * C(i)$$

Then using the carry operator

$$(G'', P'') \diamondsuit (G', P') = (G''+G'\cdot P'', P'\cdot P'')$$

Once we get all the carry's we can get the sum by the formula

$$S(i) = P(i)$$

$\bigcirc$   $C(i)$

# Circuit Diagram(s):

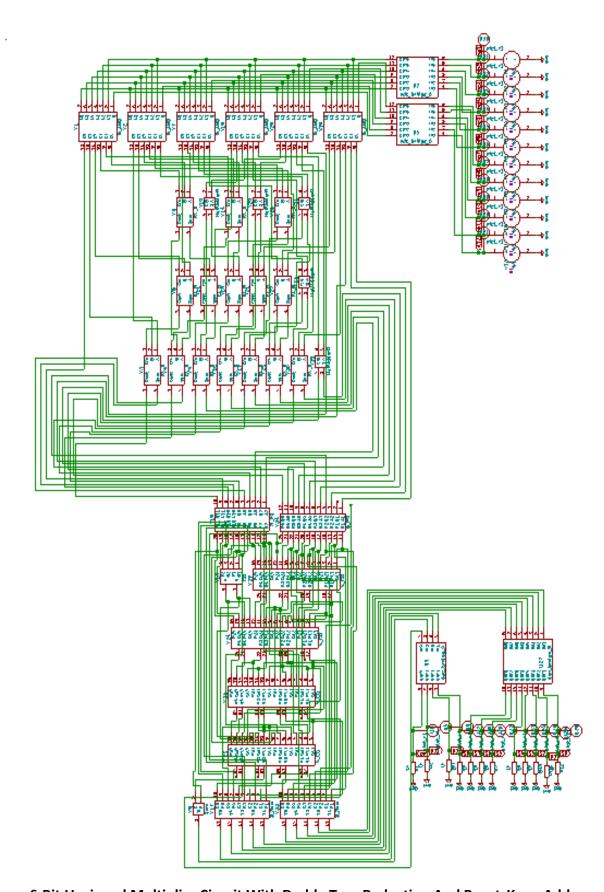

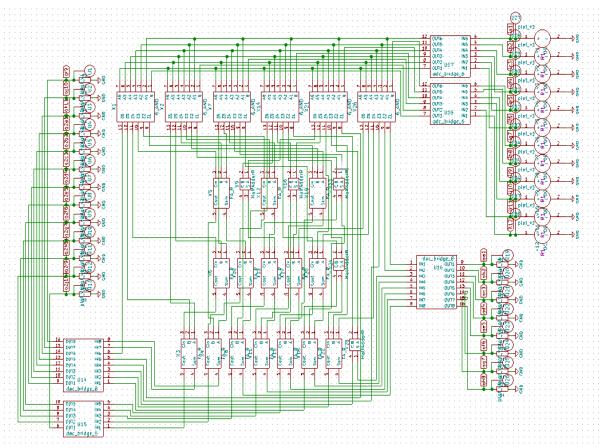

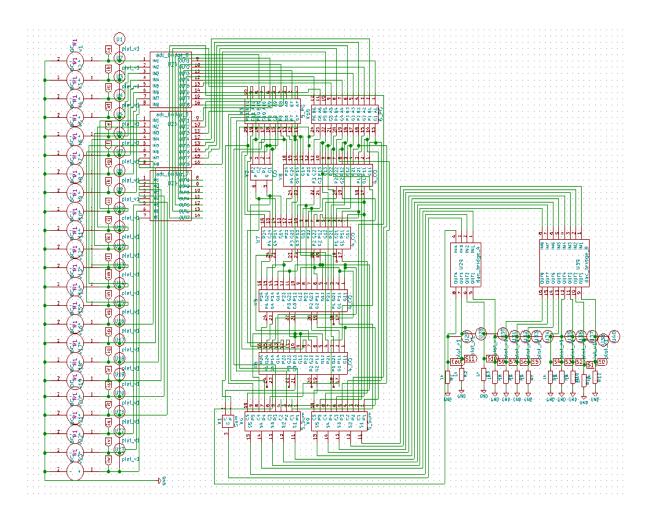

6-Bit Unsigned Multiplier Circuit With Dadda Tree Reduction And Brent-Kung Adder

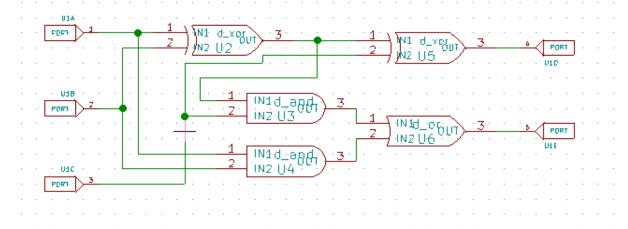

#### Dadda Tree Reduction Multiplier and It's Sub-circuit's:

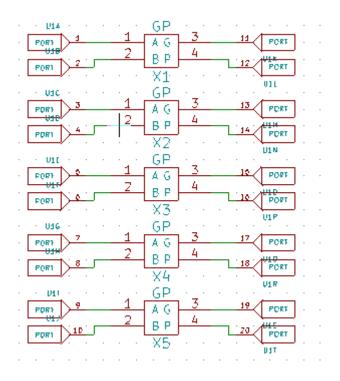

#### **6x6 Dadda Tree Reduction**

6 And Gates for Generating the Partial Products

6\_and (AndArrayTest)

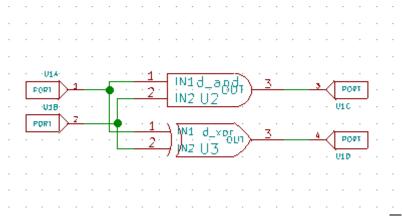

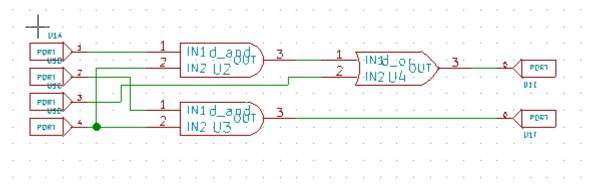

### **Full Adder**

### fa-r (Full\_Adder\_R)

**Half Adder**

# halfadderr (HalfAdderR)

\*Note: Sub-Circuit Abbreviation (Sub-Circuit File Name in the Project Files)

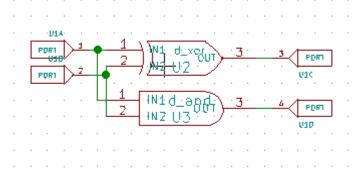

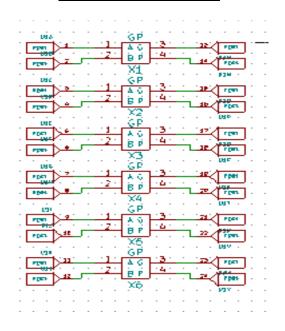

#### Brent Kung Adder and It's Sub-circuit's:

### 11-bit Brent Kung Adder

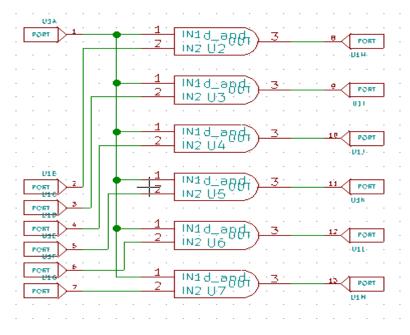

<u>6 Propagate and Generate Blocks</u> <u>6 PG (Gen&PropArray)</u>

## <u>5 Propagate and Generate Blocks</u> <u>5 PG (Gen&PropArray)</u>

Propagate and Generate Block

GP (Gen&Prop)

\*Note: Sub-Circuit Abbreviation (Sub-Circuit File Name in the Project Files)

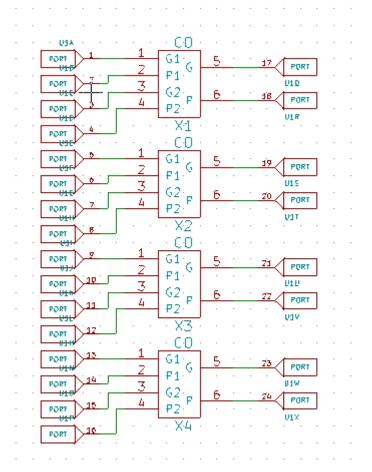

# 4 Carry Operator Blocks 4 CO (CarryOperatorArray)

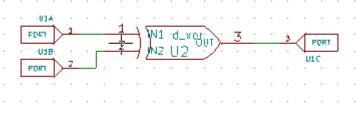

Carry Operator Block

CO (CarryOperatorR)

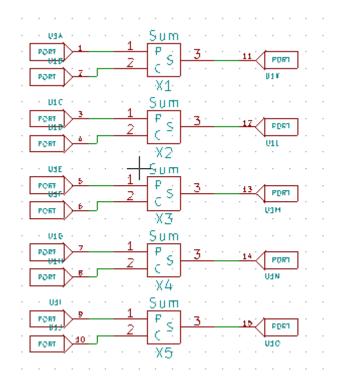

<u>5 Sum Blocks</u> <u>5 SUM (SumArray)</u>

Sum Block SUM (SumR)

\*Note: Sub-Circuit Abbreviation (Sub-Circuit File Name in the Project Files)

# Results (Input, Output waveforms and/or Multimeter readings):

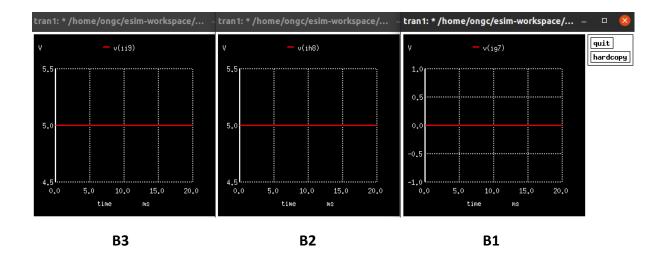

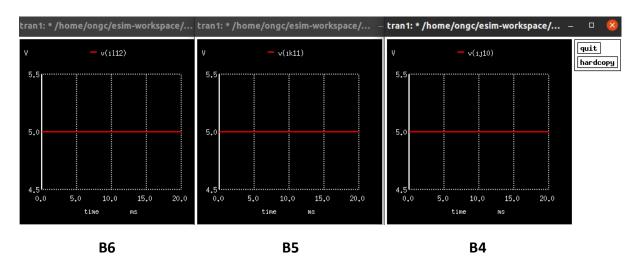

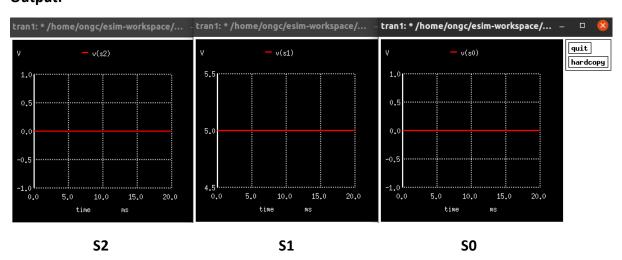

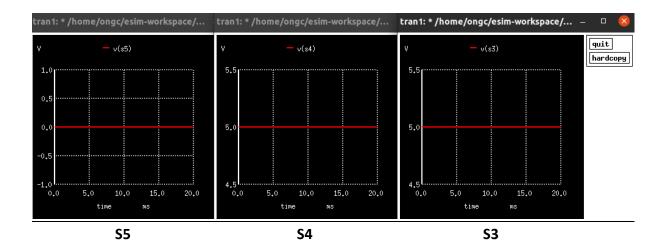

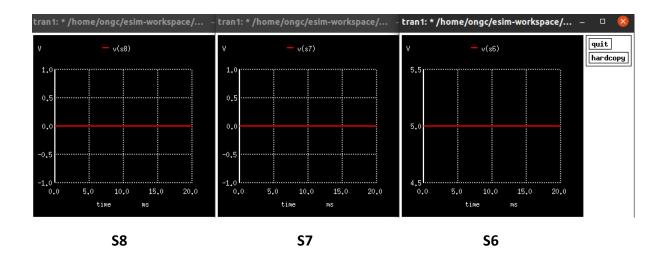

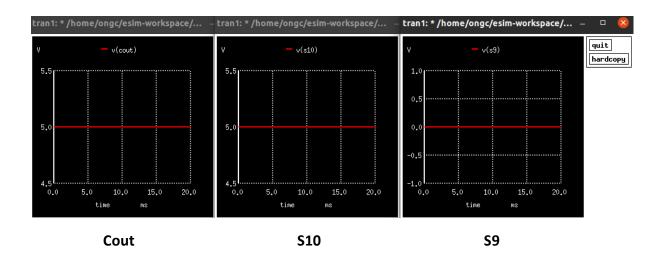

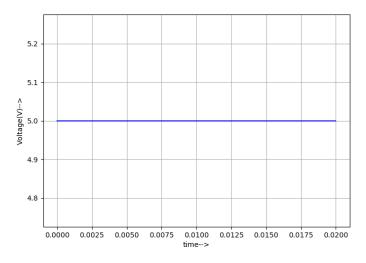

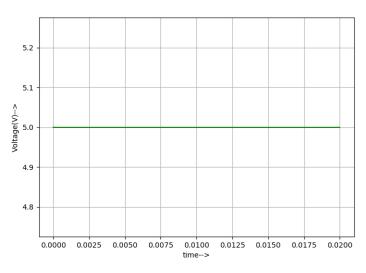

We will be multiplying to 2 6-bit binary numbers to verify our simulation

A = 110011

B = 111110

A X B = 110011 X 111110 = 110001011010

#### Ngspice:

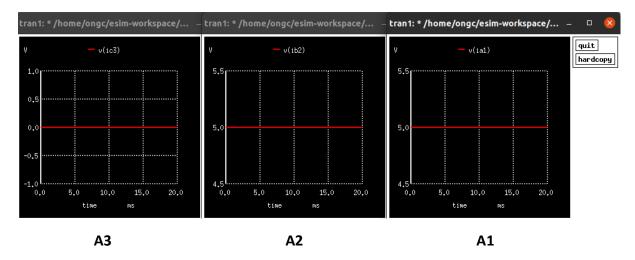

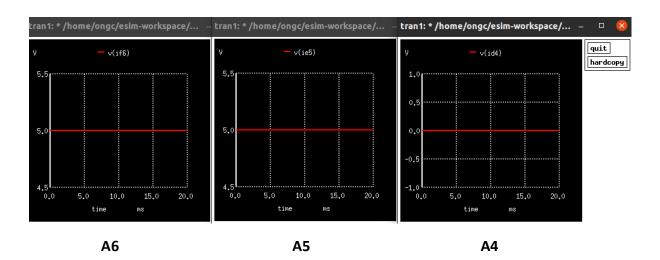

#### Input:

#### **Output:**

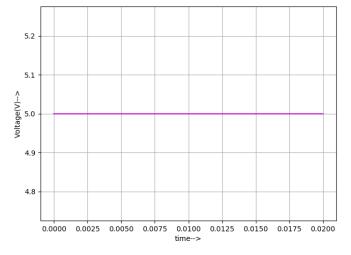

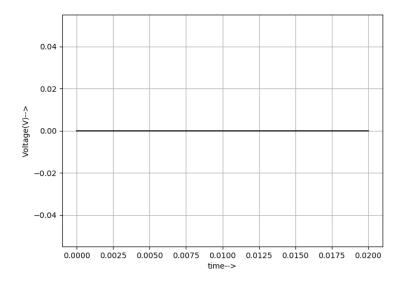

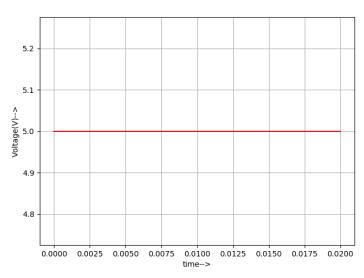

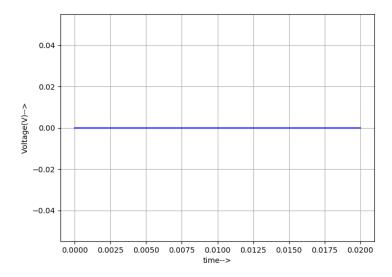

# **Python Plots:**

# Input:

### **A1**

# **A2**

#### Α4

### **A5**

В1

**B2**

**B4**

**B5**

# **Output:**

S0

**S1**

**S3**

**S4**

**S6**

**S7**

**S9**

**S10**

Cout

# Source/Reference(s):

- 1. <a href="https://en.wikipedia.org/wiki/Brent%E2%80%93Kung\_adder">https://en.wikipedia.org/wiki/Brent%E2%80%93Kung\_adder</a>

- 2. <a href="https://www.ijitee.org/wp-content/uploads/papers/v8i9S3/I31300789S319.pdf">https://www.ijitee.org/wp-content/uploads/papers/v8i9S3/I31300789S319.pdf</a>

- 3. <a href="https://en.wikipedia.org/wiki/Dadda\_multiplier">https://en.wikipedia.org/wiki/Dadda\_multiplier</a>