# 3 BIT Serial Input Parallel Output Shift Register

#### Introduction

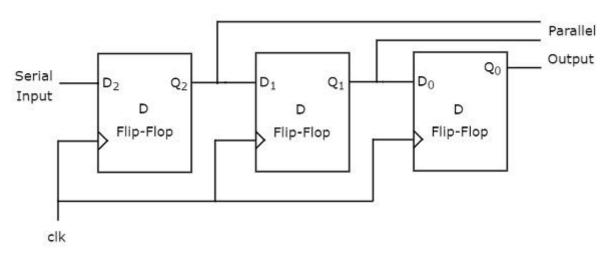

The sequential device loads the data present on its inputs and then moves or "shifts" it to its output once every clock cycle, hence the name **Shift Register**. A *shift register* basically consists of several single bit "D-Type Data Latches", one for each data bit, either a logic "0" or a "1", connected together in a serial type daisy-chain arrangement so that the output from one data latch becomes the input of the next latch and so on. In Serial **In Parallel Out (SIPO) shift registers**, the data is stored into the register serially while it is retrieved from it in parallel-fashion. Figure 1 shows an 3-bit synchronous **SIPO shift register** sensitive to the positive edge of the clock pulse. Here the data word which is to be stored (Data in) is fed serially at the input of the first flipflop( $D_1$  of  $FF_1$ ). It is also seen that the inputs of all other flip-flops (except the first flip-flop  $FF_1$ ) are driven by the outputs of the preceding ones say for example, the input of  $FF_2$  is driven by the output of  $FF_1$ . In this kind of shift register, the data stored within the register is obtained as a parallel-output data word (Data out) at the individual output pins of the flip-flops ( $Q_1$  to  $Q_3$ ).

Fig1: Block Diagram of 3-Bit Right Shift SIPO Register

In general, the register contents are cleared by applying high on the reset pins of all the flip-flops at the initial stage. After this, the first bit,  $B_1$  of the input data word is fed at the  $D_1$  pin of  $FF_1$ . This bit ( $B_1$ ) will enter into  $FF_1$ , get stored and thereby appears at its output  $Q_1$  on the appearance of first leading edge of the clock. Further at the second clock tick, the bit  $B_1$  right-shifts and gets stored into  $FF_2$  while appearing at its output pin  $Q_2$  while a new bit,  $B_2$  enters into  $FF_1$ . Similarly at each clock tick the data within the register moves towards right by a single bit while a new bit of the input word enters into the register. Meanwhile one can extract the bits stored within the register in parallel-fashion at the individual flip-flop outputs.

In the right-shift SIPO shift-register, data bits shift from left to right for each clock tick. However if the data bits are made to shift from right to left in the same design, then we get a left-shift SIPO shift-register.

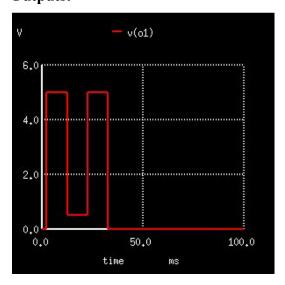

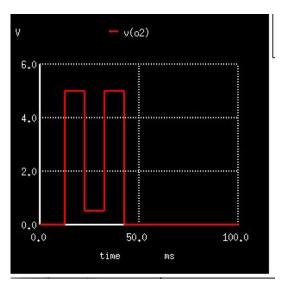

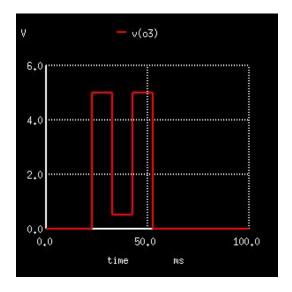

# **NgSpice Plots**

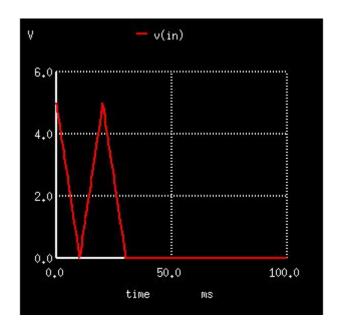

### **Input:**

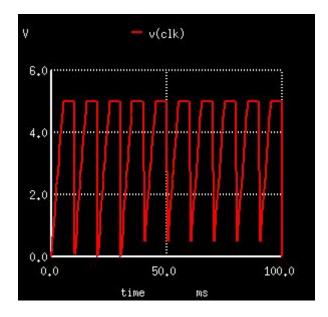

# Clock:

# **Outputs:**

#### **References:**

https://www.electronics-tutorials.ws/sequential/seq\_5.html https://www.electrical4u.com/serial-in-parallel-out-sipo-shift-register/