Dr.Maheswari.R

### TITLE OF THE EXPERIMENT -

### **4 BIT SYNCHRONOUS SERIAL IN SERIAL OUT SHIFT REGISTER**

#### Abstract:

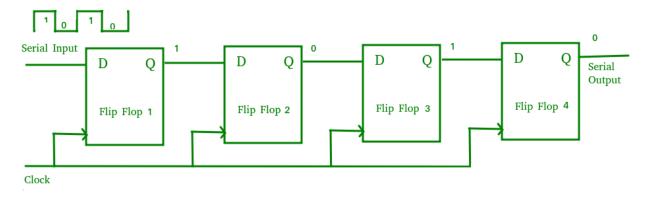

Shift Register is a group of flip flops used to store / move multiple bits of data. In Serial-in to Serial-out (SISO) shift register the data is shifted serially "IN" and "OUT" of the register, one bit at a time in either a left or right direction under clock control. It allows serial input i.e. one bit after the other through a single data line and produces a serial output. There is only one output, the data leaves the shift register one bit at a time in a serial pattern. The circuit consists of four D flip-flops which are connected in a serial manner. All these flip-flops are synchronous with each other since the same clock signal is applied to each flip flop.

### **Circuit Diagram:**

# Truth Table:

| Operation of the Shift-right Register |       |            |            |            |                                             |

|---------------------------------------|-------|------------|------------|------------|---------------------------------------------|

| Timing pulse                          | $Q_A$ | $Q_{B}$    | $Q_{c}$    | $Q_D$      | Serial output at $Q_{\scriptscriptstyle D}$ |

| Initial value                         | 0_    | 0 🔪        | 0_         | 0          | 0                                           |

| After 1 <sup>st</sup> clock pulse     | 1     | <b>A</b> 0 | <b>A</b> 0 | <b>^</b> 0 | 0                                           |

| After 2 <sup>nd</sup> clock pulse     | 1     | 1          | 0          | 0          | 0                                           |

| After 3 <sup>rd</sup> clock pulse     | 0     | 1          | 1          | 0          | 0                                           |

| After 4 <sup>th</sup> clock pulse     | 1     | 0          | 1          | 1          | 1                                           |

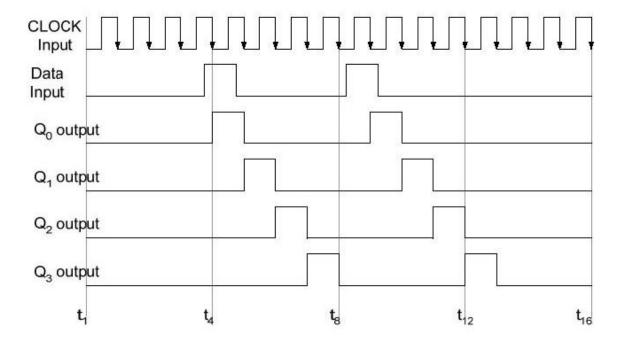

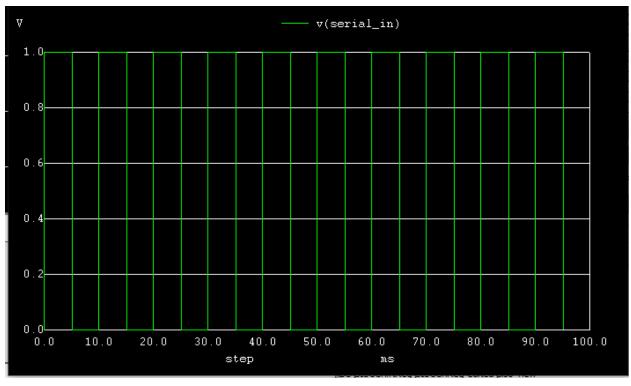

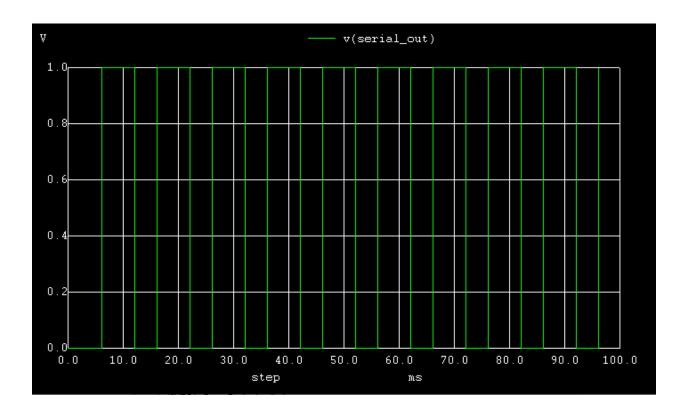

# Timing Diagram:

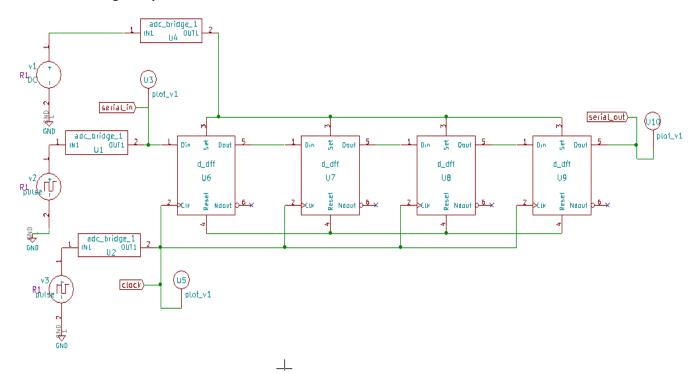

# eSim Required Components :

| Synchronous up counter |                               |  |  |

|------------------------|-------------------------------|--|--|

| Component Name         | Туре                          |  |  |

| d_dff                  | d flip flop                   |  |  |

| clock                  | clock input                   |  |  |

| DC                     | dc voltage source for logic 1 |  |  |

## **ESIM Circuit design snapshot:**

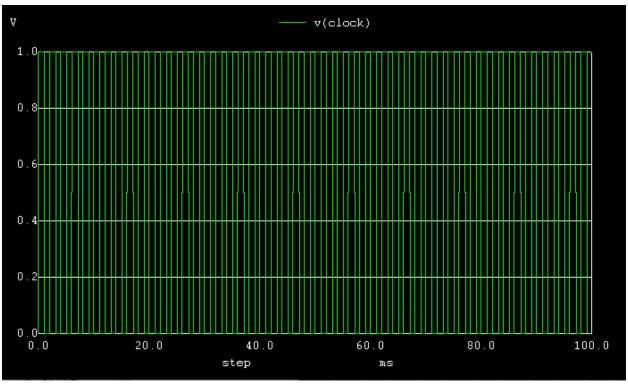

## OUTPUT -

## **References:**

- https://www.electrical4u.com/serial-in-serial-out-siso-shift-register/

- https://www.geeksforgeeks.org/shift-registers-in-digital-logic/