#### TITLE OF THE EXPERIMENT

#### DESIGN OF FOUR BIT VEDIC MULTIPLIER USING ESIM

#### **THEORY**

The performance of the multiplier determines the system performance, because the multiplier is slowest element in the system. Multiplication is one of the major operation in arithmetic and logical operations and multiplier is used in many applications like FFT, DFT, Image enhancement, DWT etc,. The multiplication speed influences the processor speed, so the speed of the multiplication should be high. There is one such promising solution i.e., Vedic multiplier. Vedic multiplier is designed using Vedic mathematics. Vedic mathematics is an ancient system of mathematics, which is formulated by Sri Jagadguru Bharathi Krishna Tirthaji (1884-1960). The word Vedic is obtained from the word —Veda|| which gives the meaning of power house of knowledge and devine.

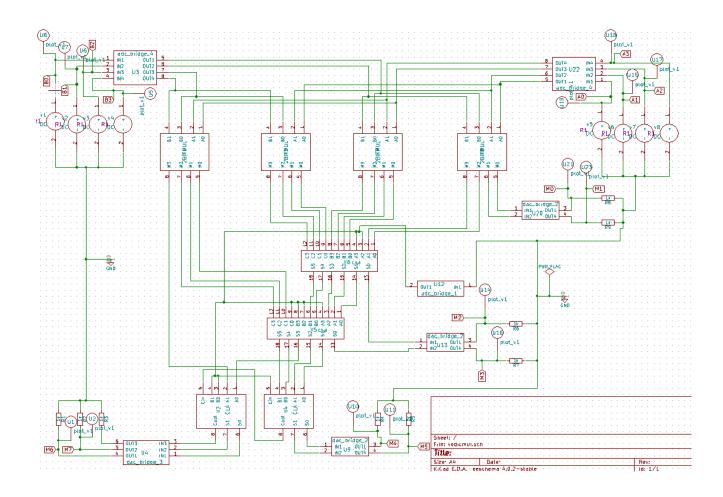

#### **Schematic Diagram**

The schematic diagram of four bit vedic multiplier is shown below. It is done using subcircuits of 2X2 Multipliers, Carry save adder, Ripple carry adder.

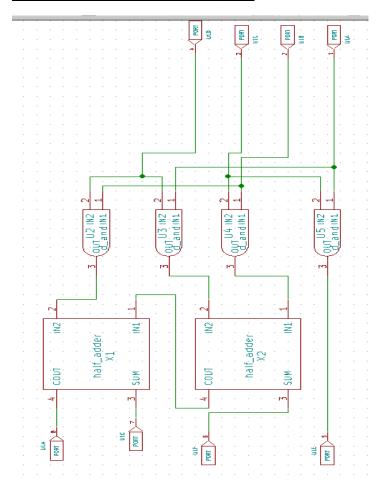

## **Subcircuit of 2X2 Multiplier**

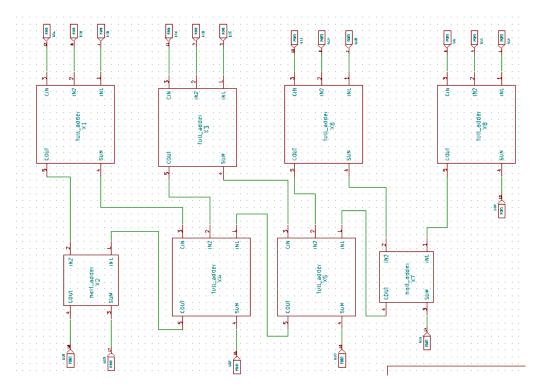

# **Subcircuit of Carry Save Adder**

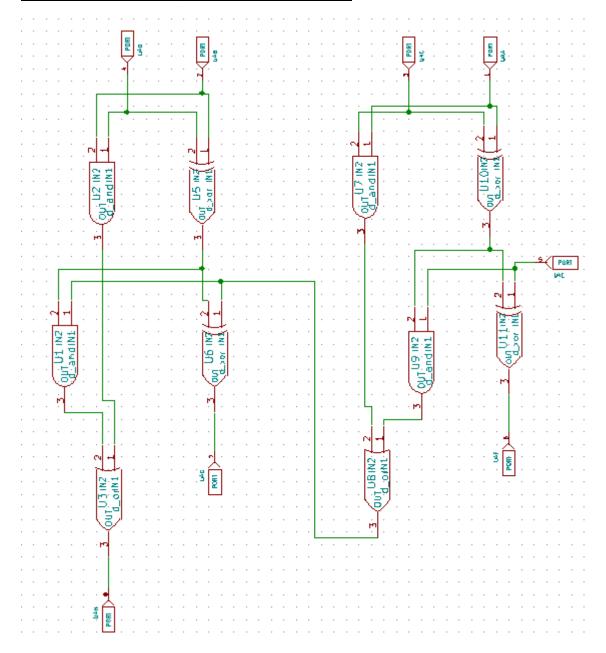

## **Subcircuit of Carry Look Ahead Adder**

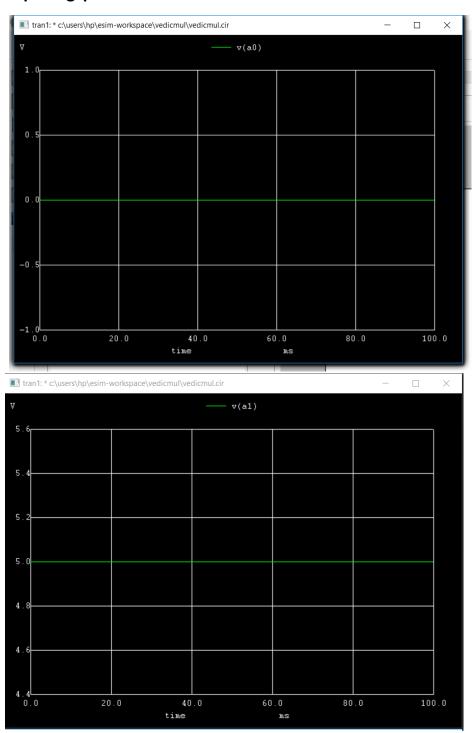

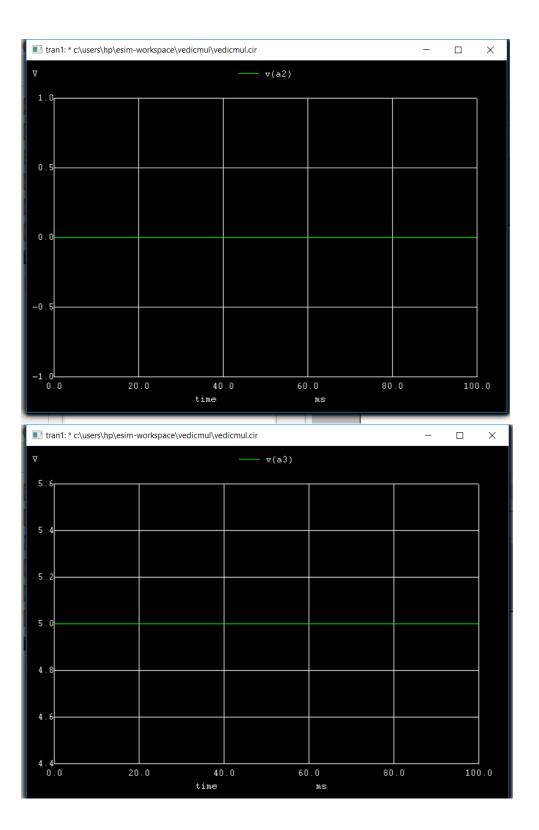

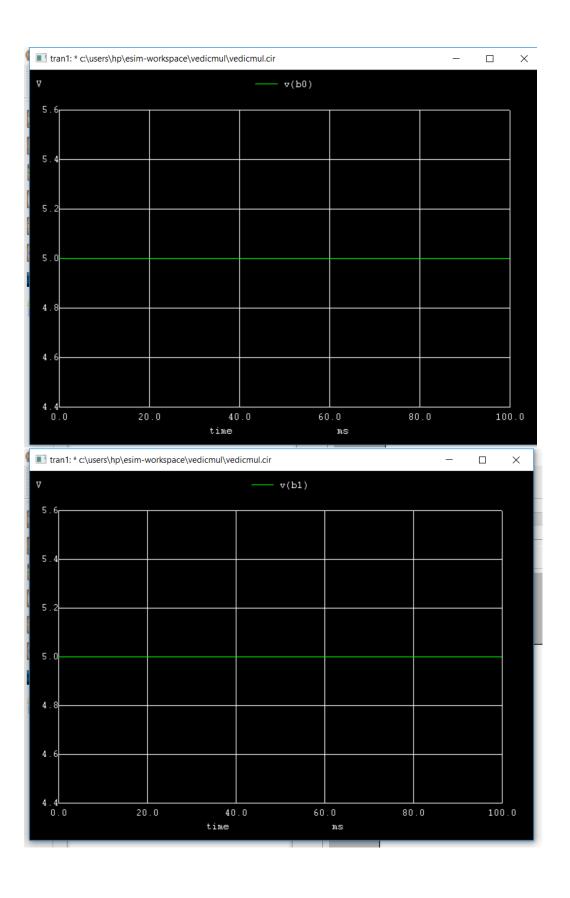

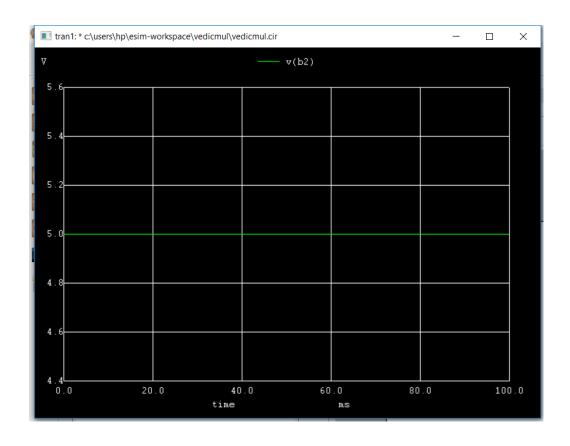

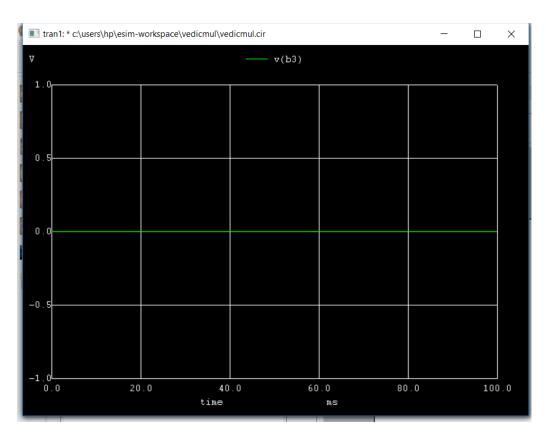

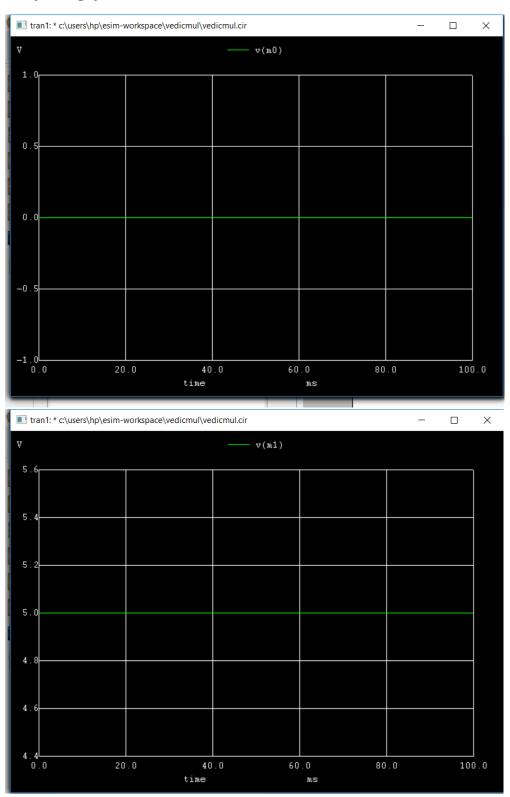

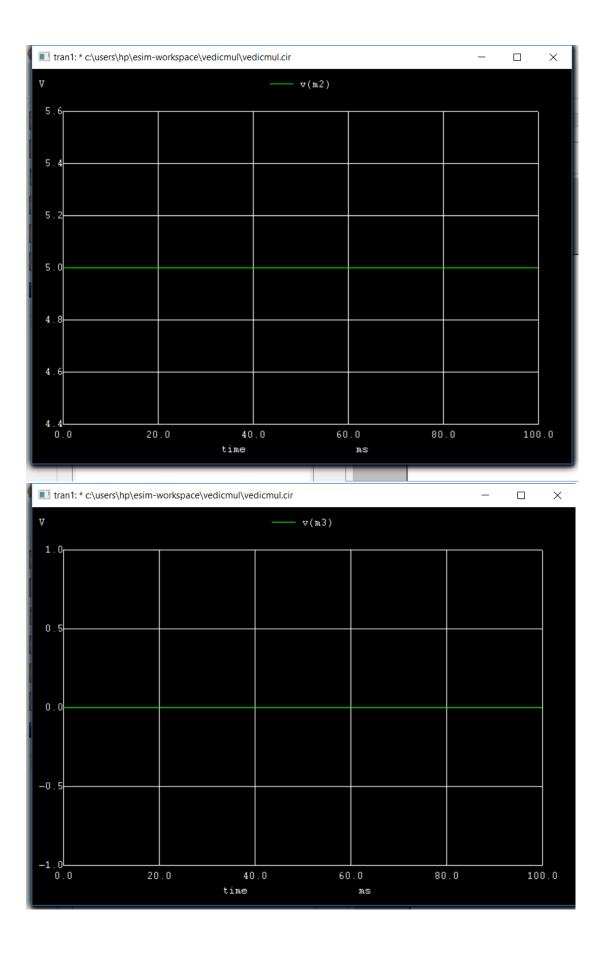

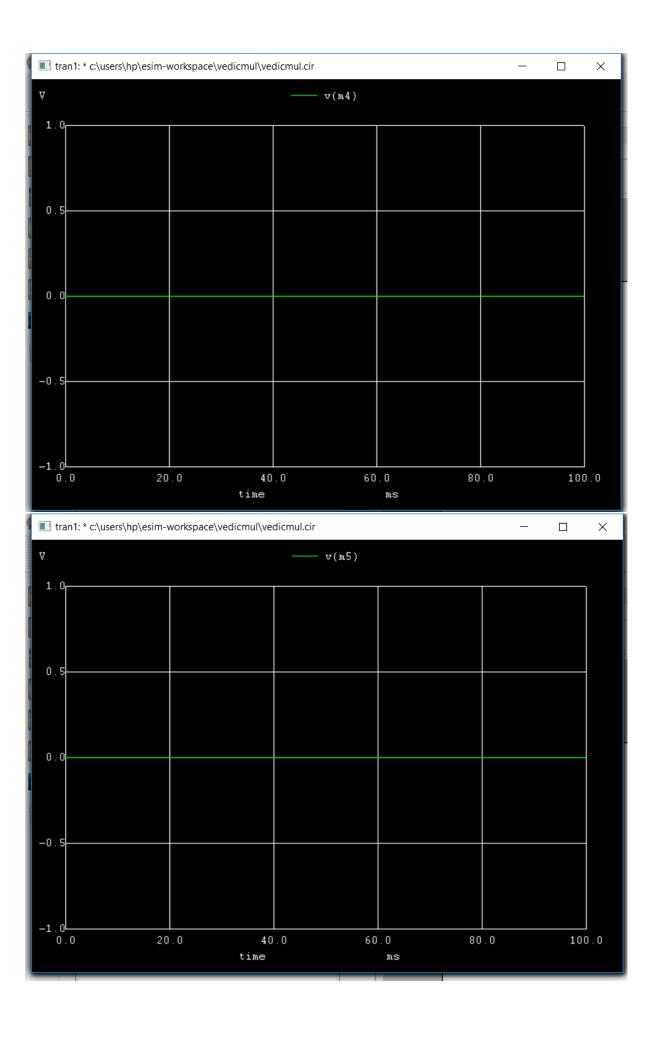

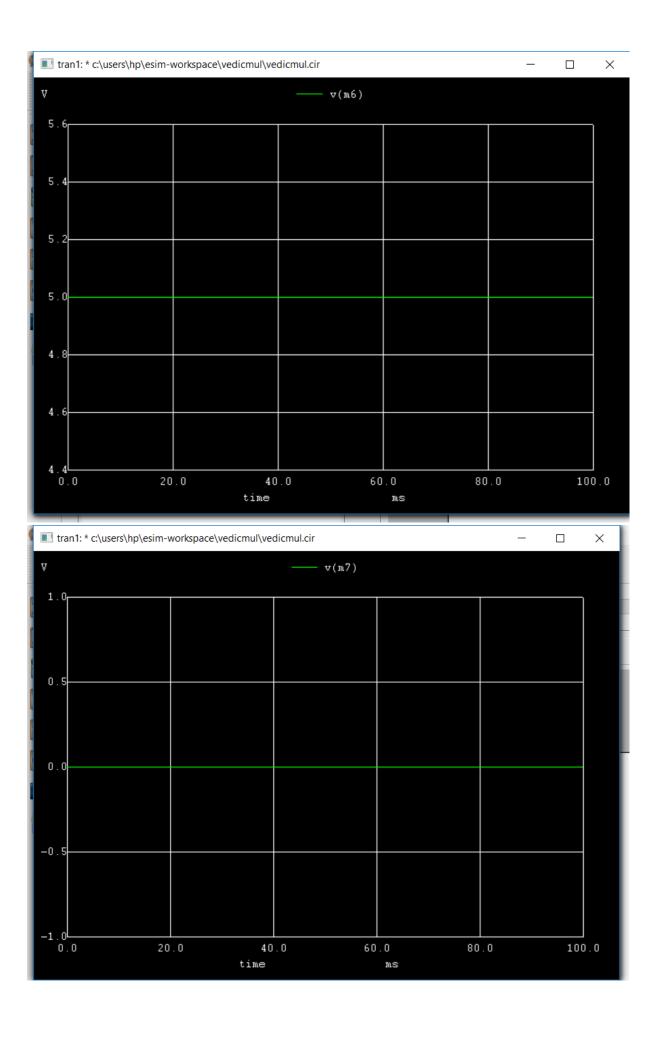

### **Input Ngspice Plots:**

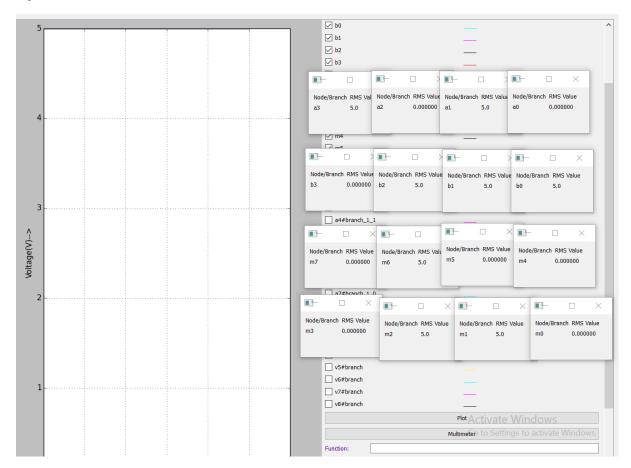

## **Output Ngspice Plots:**

### **Python Plot:**

#### **References:**

https://www.researchgate.net/figure/bit-multiplier-design1\_fig7\_273137511