## Title :- 4 BIT BINARY FULL ADDER

### Theory:-

These full adders perform the addition of two 4-bit binary numbers.

The sum S outputs are provided for each bit and the resultant carry (Cout) is obtained from the fourth bit.

But these adderscontain one special block for the carry bit which feature full internal look ahead across all four bits. This provides the system designer with partial lookahead performance at the economy and reduced package count of a ripple-carry implementation. The adder logic, including the carry, is implemented in its true form meaning that the end-around carry can be accomplished without the need for logic or level inversion.

Here a0,a1,a2,a3 and b0,b1,b2,b3 are the 4 bit binary numbers to be added. Cin is the input carry bit. s0,s1,s2,s3 are the result bits and Cout is the output carry bit.

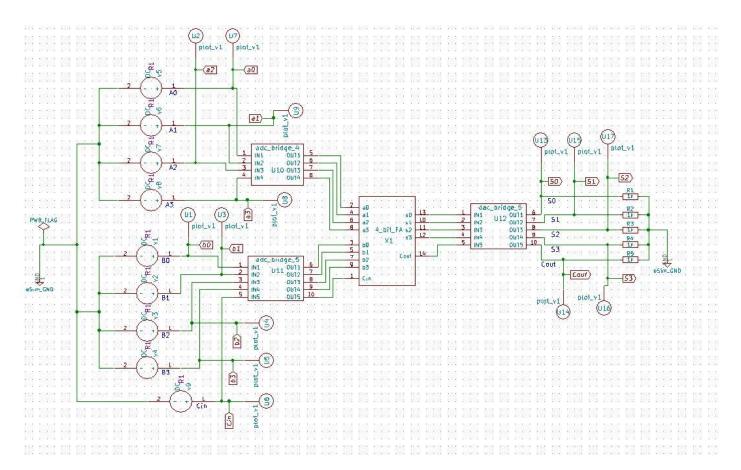

## Schematic Diagram:-

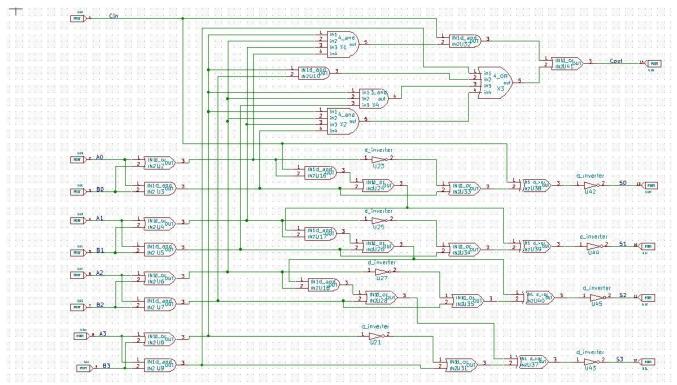

## Subcircuit schematic for 4\_bit\_FA block:-

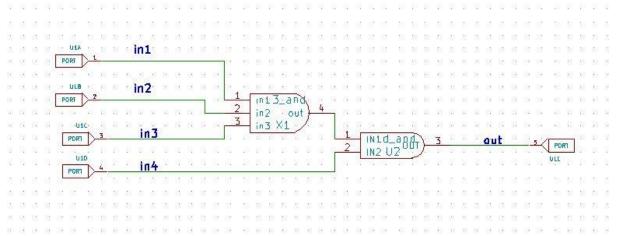

## Subcircuit schematic for "3\_and" gate :-

|       |  | 2   | č.  |     |   |     |    | 1   |     | 200  |     | 1007 | 3       |   |     | i,   |     | ŝ,     | 1    | ŗ   | ŧ. |      |           | S.  |           |     |      |    | 100     | ÷.                |                 | 1  | 1     |     | į.    |    | ţ, |       |     |

|-------|--|-----|-----|-----|---|-----|----|-----|-----|------|-----|------|---------|---|-----|------|-----|--------|------|-----|----|------|-----------|-----|-----------|-----|------|----|---------|-------------------|-----------------|----|-------|-----|-------|----|----|-------|-----|

|       |  | Ē   | -   | N D | ι | 5.8 |    | in) |     | 20   | 1   | -    | IN1     | d | ap  | E C  |     | 3      | 1222 |     |    |      | 1000      |     | 1000      |     | 1000 | S  | 122     |                   |                 | 8  |       |     | 0.00  | į, |    |       |     |

|       |  | Г   | PDR |     | 7 | Ę., | Ĩ. | 12  | Sea | 14   | 7   |      |         |   |     |      | E.  |        | l    |     | Th | Ld   | _0)       | À   | N N       | 3   | 2020 | 2  | 2002    |                   | 0               | ut | ģ.    |     |       |    | 1  |       |     |

| 282   |  |     | ŝ   |     |   |     |    | - 2 | -   | 5    | 100 | 2    |         | 3 | 355 | 8    | 63  | 2      |      | Z   | Ű. | 12 1 | 13,       | 201 | Ę.        | 1.1 | - 60 | 10 | - 50    | 30                | e <sup>se</sup> |    | δ     | 600 | s - 1 | 0  | -  | ACI . | 623 |

| 10.04 |  |     | in. | 12  |   | 1.  |    | 100 | 222 | - 53 | 24  | - 53 | 1       | 2 | 23  | 2    | 100 |        |      | 100 | 8  |      | 10        |     | 4         |     | - 23 | 1  | - 5     | ÷.,               | 4               |    | 8     |     |       |    |    | <br>  |     |

|       |  | E   | POR | ED. | , |     |    | in. | 5   | 20   | 88  | ->>  | (60)    | 2 | 8,2 | 1    | 128 | 8      | 1    |     | į  |      | 12.52     |     |           | 1.1 | 2222 | 1  | 1000    | 3                 | 100             |    | 100   |     | 1000  |    |    |       |     |

|       |  | - [ | POR | Ë.  | 1 |     |    | in. | 5   | 2002 |     | 25.0 | а)<br>Ф |   | 10  | 1000 |     | 8<br>8 | 100  |     | -  |      | 2552 X522 |     | 1000 NO.0 |     | 1012 |    | No. No. | 9.4<br>1.4<br>9.4 |                 | :  | 100 A |     |       |    |    |       |     |

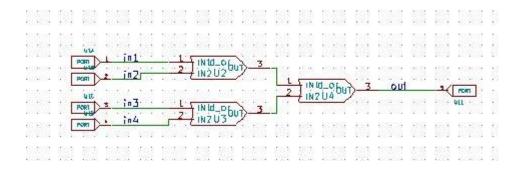

## Subcircuit schematic for "4\_and " gate :-

# Subcircuit Schematic for "4\_OR" gate :-

**Simulation Results:-**

**NGSPICE PLOTS:-**

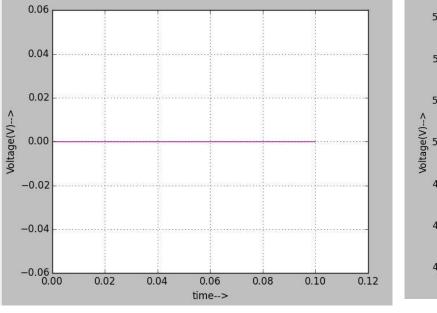

Input:-

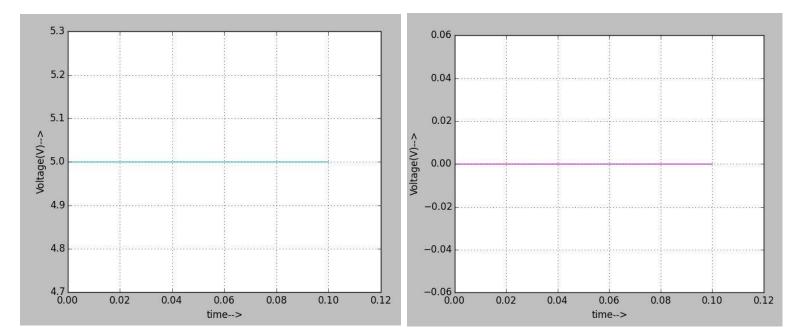

a0( v5 )

a1(v6)

a2 ( v7 )

b0(v1)

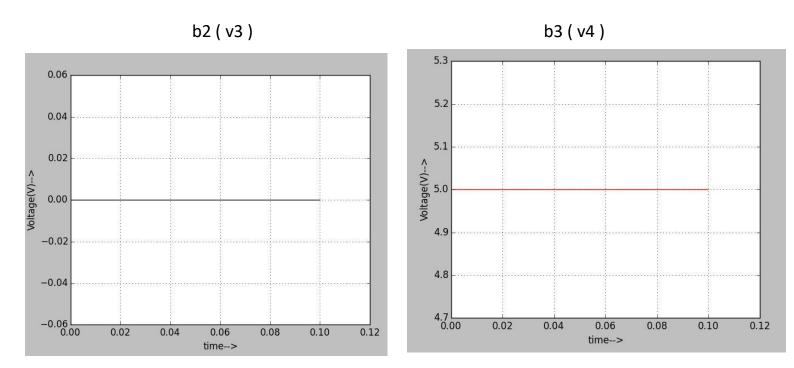

b2 ( v3 )

Cin ( v9 )

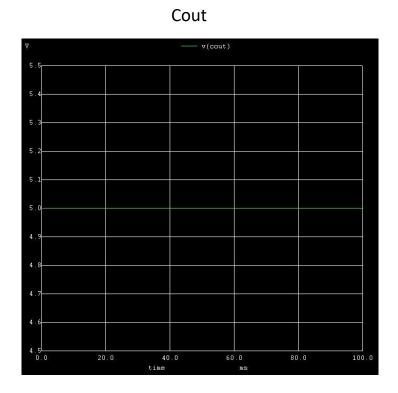

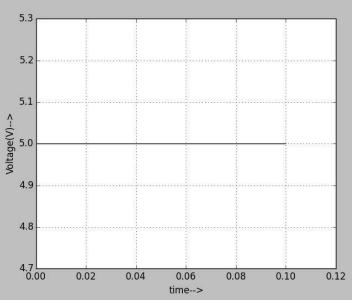

# Output:-

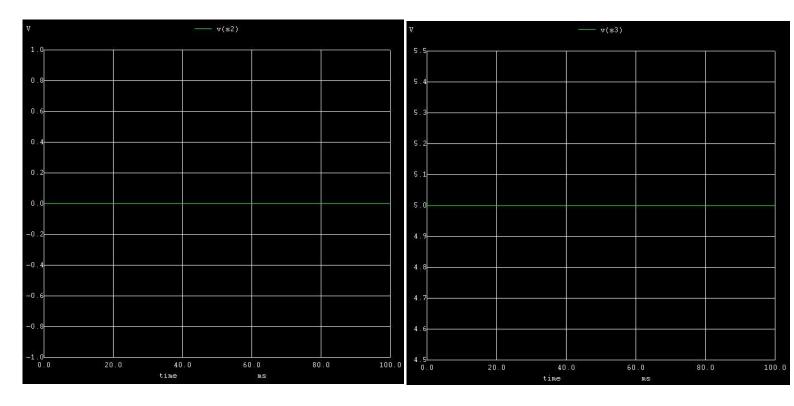

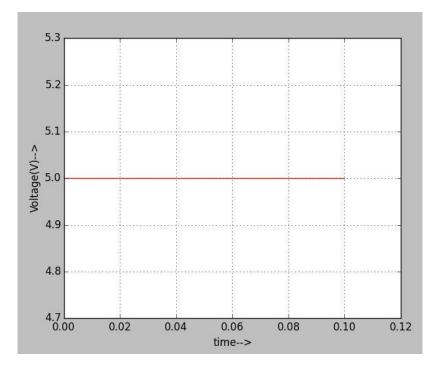

s2

s3

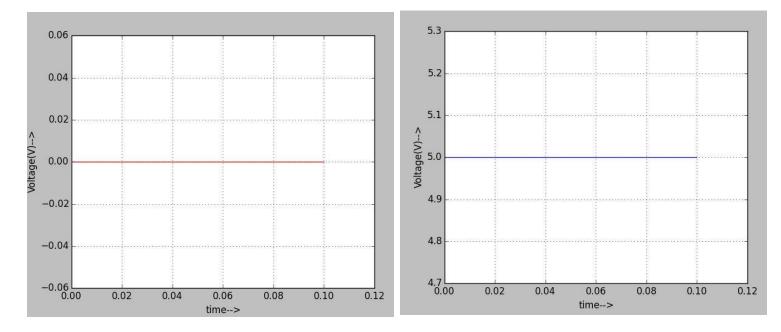

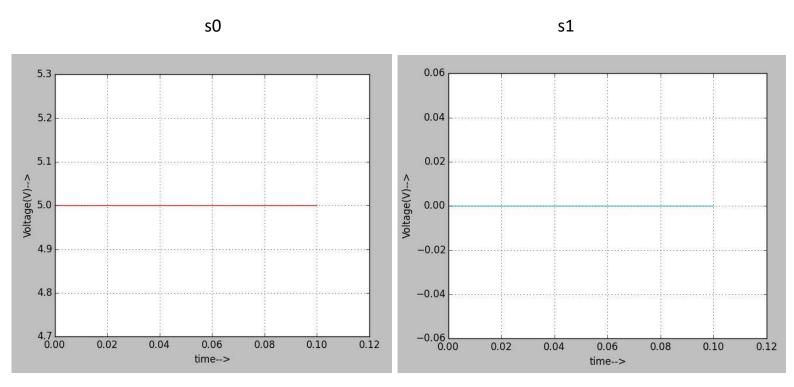

**PYTHON PLOTS:-**

Input:-

a0( v5 )

a2 ( v7 )

b0(v1)

Cin ( v9 )

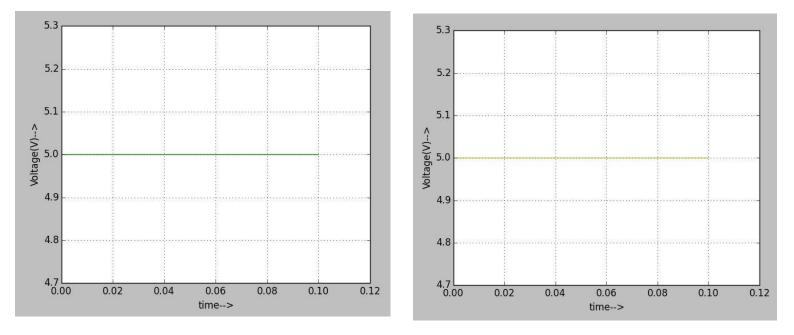

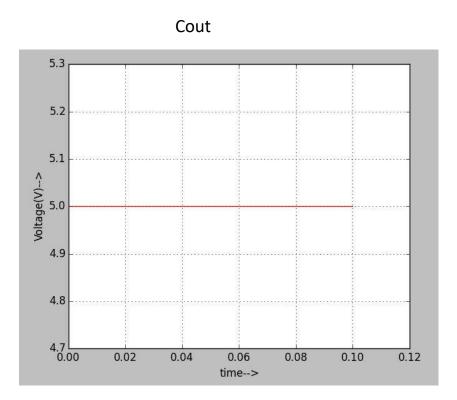

Output:-

INPUT :-

a[3:0]:1110

b[3:0] :1001

Cin : 1

OUTPUT :-

Cout : 1

s[3:0]:1001

#### **REFERENCES:-**

1) <u>https://en.wikibooks.org/wiki/Practical\_Electronics/IC/4008#/media/File:4008\_Gate-level\_Diagram.svg</u>