#### **4T XOR GATE**

#### **Theory:**

The important gates in the digital circuits are exclusive-OR and exclusive-NOR gates. Nowadays a low power XOR /XNOR gates are required. This paper proposes the new set of low power 4 – transistor XOR gate. The new XOR gate consistently consumes less power than the former XOR gate. The new XOR gate consumes up to more than three times less power than the CMOS implementation, and it has a 34% propagation delay.

The XOR gate is the basic element used in the full adder design, generating the adder circuits' basic addition operation. For proper working, the XOR gate conventionally uses 8 MOSFET. In this work, design a 4T XOR gate is considered. The application of this 4T XOR gate would now significantly reduce the full adder size and thus increase the circuit density and reduce the overall leakage.

The XOR gate is a digital logic gate that gives a true output when any two inputs are true. If either input of the XOR gate is false or both the inputs are true, the XOR gate gives a false output.

| Α | В | Υ |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

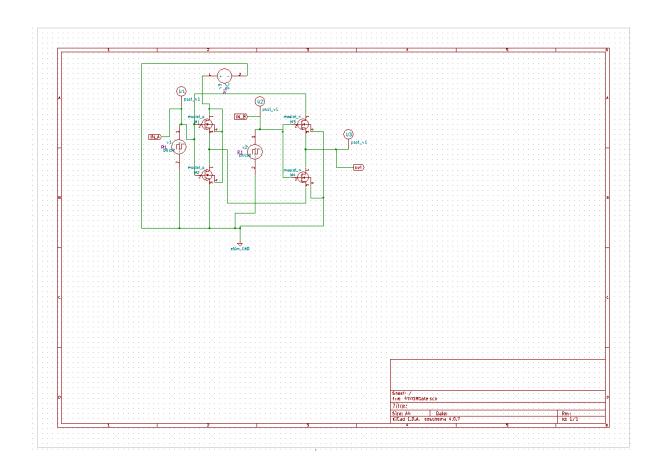

# **Schematic Diagram:**

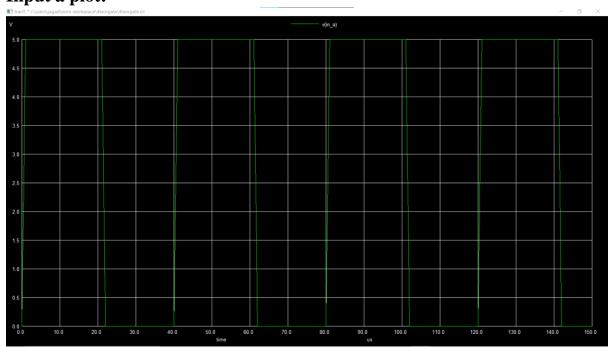

# Input a plot:

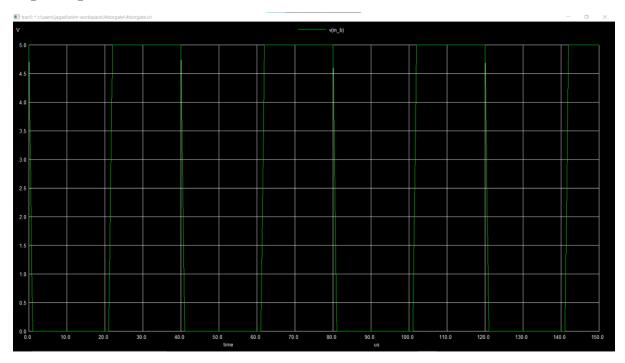

# Input b plot:

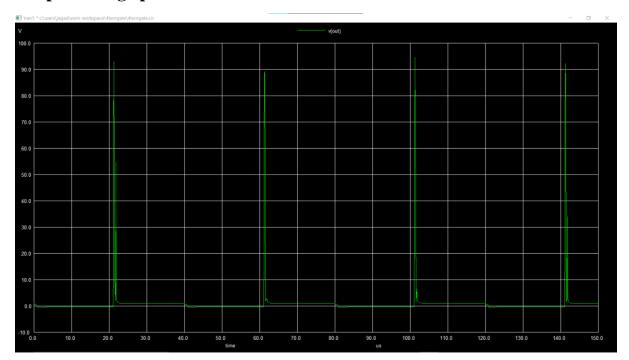

# Output voltage plot:

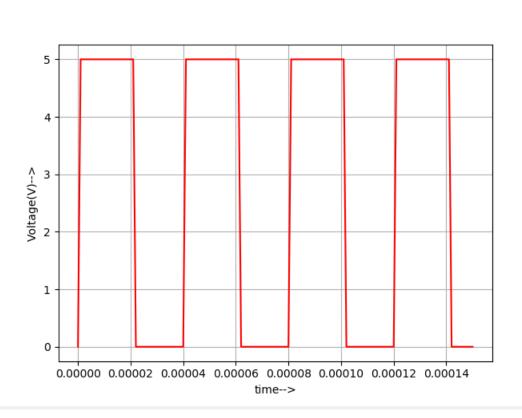

## Python input a plot:

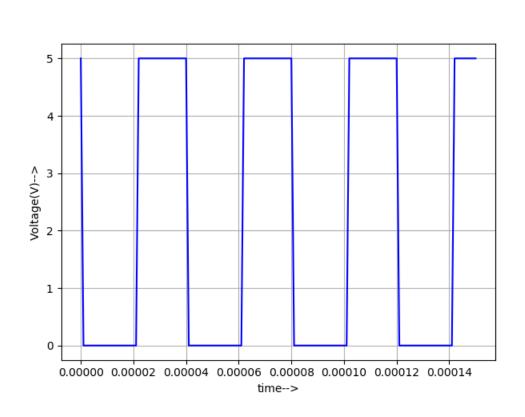

## **Python input b plot:**

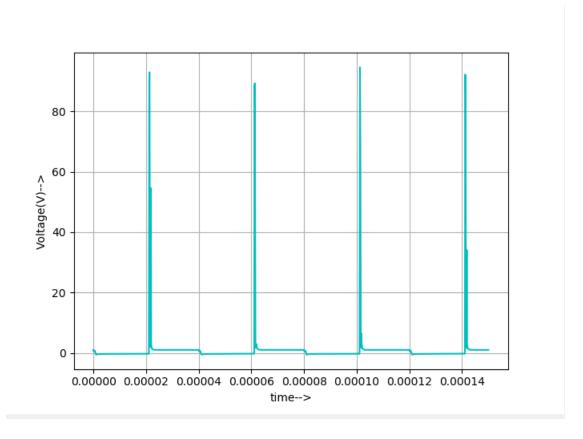

### **Python output plot:**

### **Conclusion:**

Thus we have studied the appropriate waveforms f the 4T XOR gate.

### **References:**

https://www.researchgate.net/publication/270898651\_A\_High\_Speed\_and\_Low\_Power\_8\_Bit\_x\_8\_Bit\_Multiplier\_Design\_using\_Novel\_Two\_Transist\_or\_2T\_XOR\_Gates/figures?lo=1