#### Title:- 74157 A Quad 2 line to 1 line Multiplexer

#### Theory :-

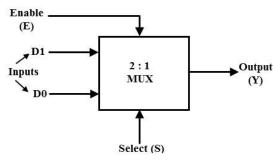

The multiplexer, shortened to "MUX" or "MPX", is a combinational logic circuit designed to switch one of several input lines through to a single common output line by the application of a control signal.

A 2-to-1 multiplexer consists of two inputs D0 and D1, one select input S and one output Y. Depends on the select signal, the output is connected to either of the inputs. Since there are two input signals only two ways are possible to connect the inputs to the outputs, so one select is needed to do these operations.

| E | S | Y  |

|---|---|----|

| 1 | Х | 0  |

| 0 | 0 | D0 |

| 0 | 1 | D1 |

**Function Table**

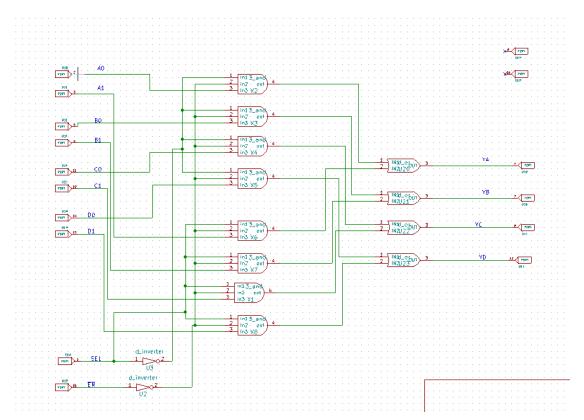

Here 74157 is a quad 2 to 1 multiplexer with one select input (S) i.e. it contains four 2:1 multiplexers. Select input S is common to all the four the multiplexers.

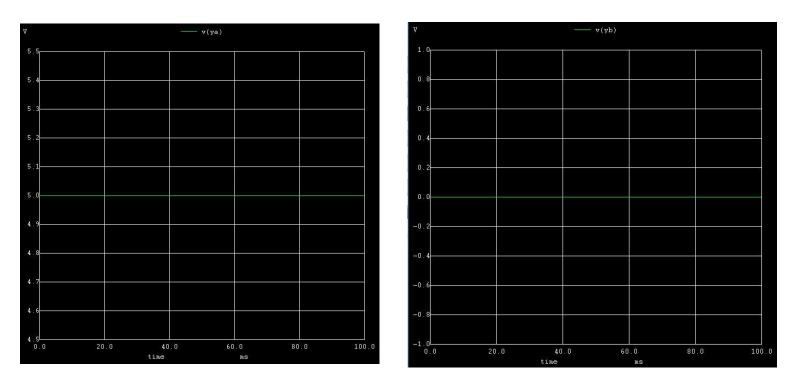

a0,a1 are the inputs and Ya is the output to the MUX1.

b0,b1 are the inputs and Yb is the output to the MUX2.

c0,c1 are the inputs and Yc is the output to the MUX3.

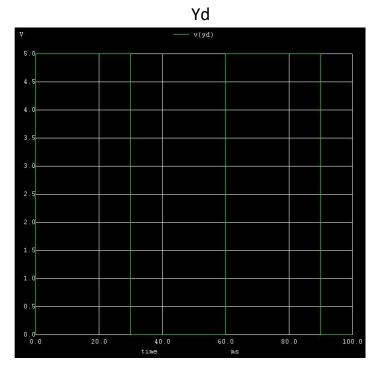

d0,d1 are the inputs and Yd is the output to the MUX4.

E is the active low enable input common to all the multiplexers.

| E | S | Ya | Yb | Yc | Yd |

|---|---|----|----|----|----|

| 1 | Х | 0  | 0  | 0  | 0  |

| 0 | 0 | a0 | b0 | c0 | d0 |

| 0 | 1 | a1 | b1 | c1 | d1 |

Function Table of 74157:-

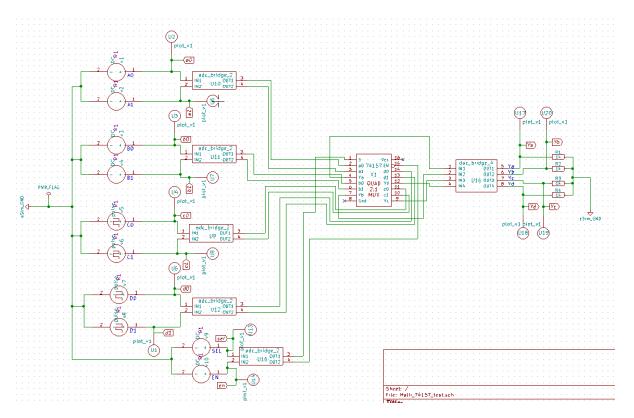

NOTE :- Here in E-SIM software, no need to connect Vcc( pin 16 ) and GND ( pin 8 ) pins to Dc source and gnd respectively, you can leave them unconnected using NO CONNECT symbol. This is because in circuit simulation softwares, we use BASIC GATES (AND, NAND etc.) they don't need Vcc and GND. As in manufacturing an IC, they use MOSFETs to implement those GATES, there MOSFETs require Vcc and Gnd

### Schematic Diagram :-

#### Subcircuit Schematic for 74157 :-

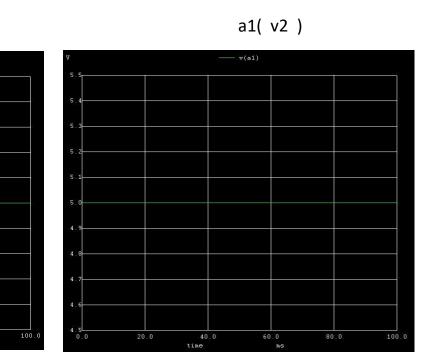

Simulation Results :-

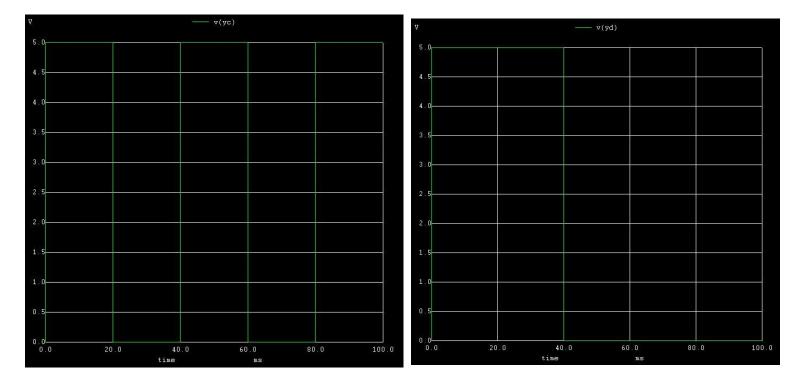

Ngspice plots

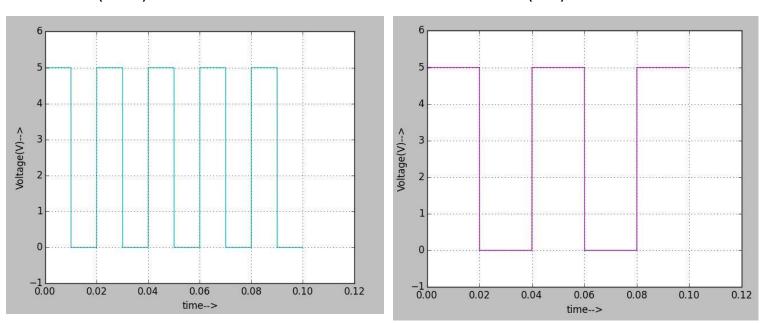

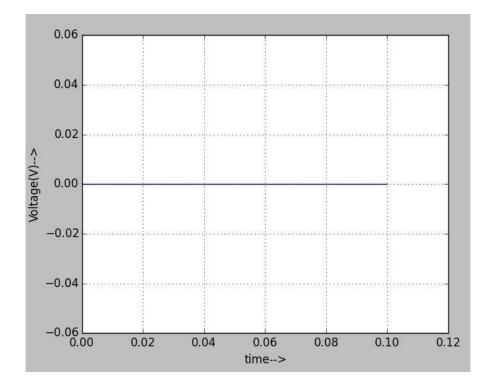

### Inputs to MUX 1

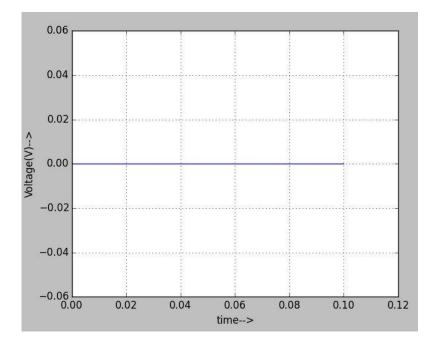

v(a0)

aO( v1 )

## Inputs to MUX 2

20.0

-0 -0

bO(v3)

40.0 time 60.0

80.0

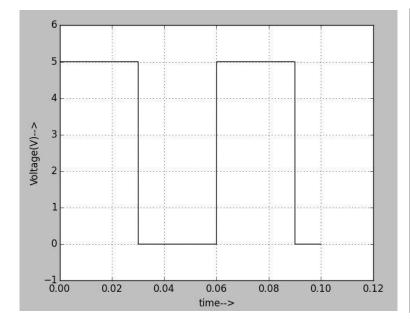

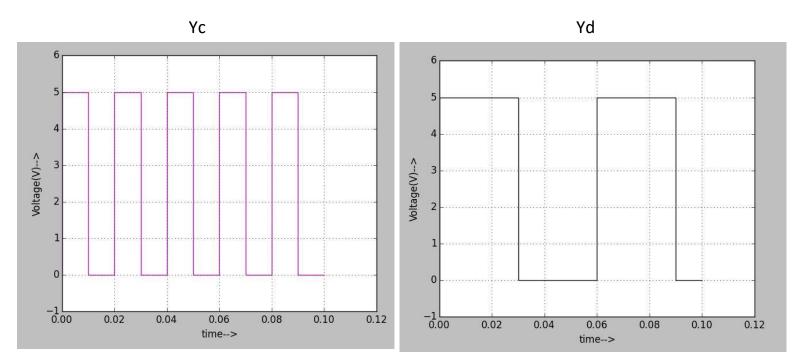

## Inputs to MUX 3

## Inputs to MUX 4

d0( v7 )

c1( v6 )

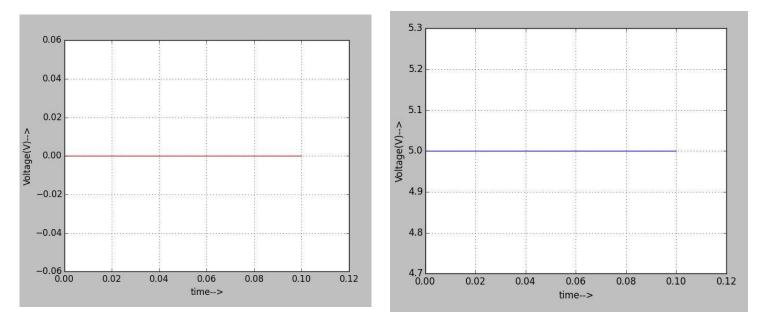

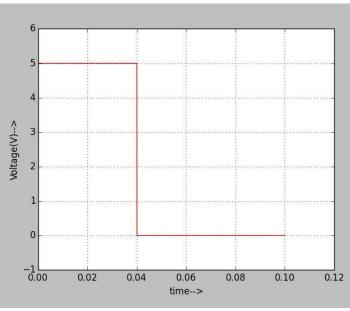

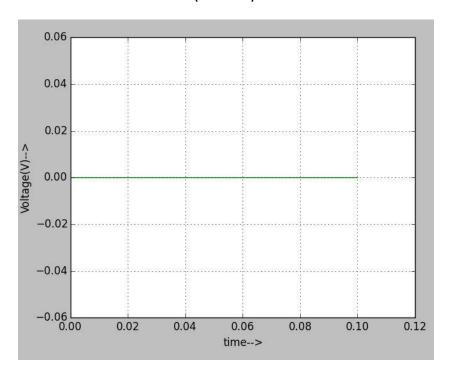

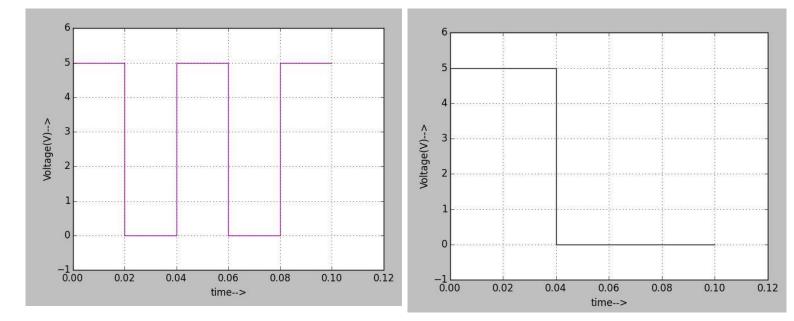

OUTPUT when SEL(S)='0' EN='0

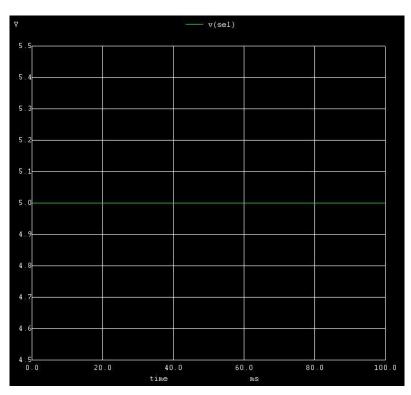

SEL S (V9=0v)

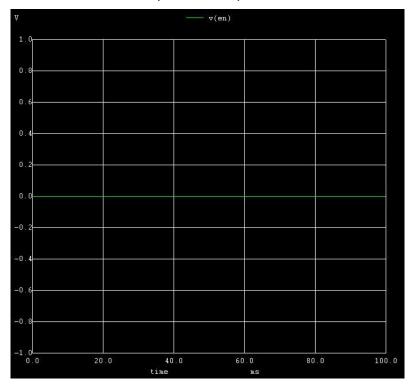

EN( v10 = 0v)

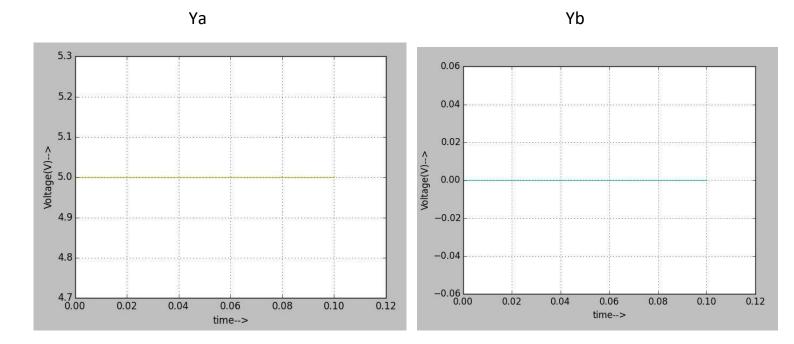

Yb

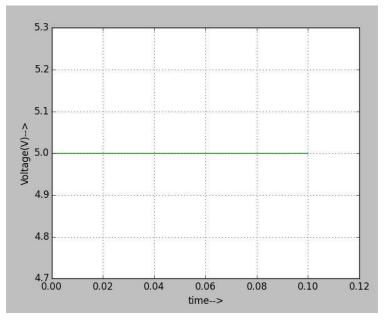

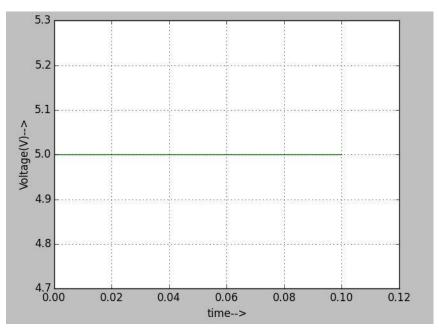

OUTPUT when SEL(S)='1' EN='0'

SEL S (V9=5v)

EN( v10 = 0v)

Ya

Yb

Yc

#### **PYTHON PLOTS**

### Inputs to MUX 1

aO( v1 )

## Inputs to MUX 2

bO(v3)

## Inputs to MUX 3

cO( v5 )

c1(v6)

Inputs to MUX 4

dO( v7 )

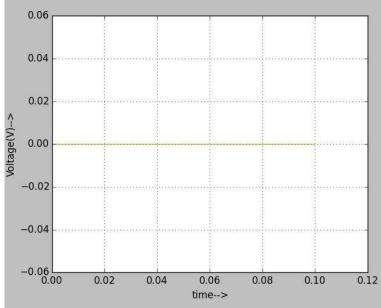

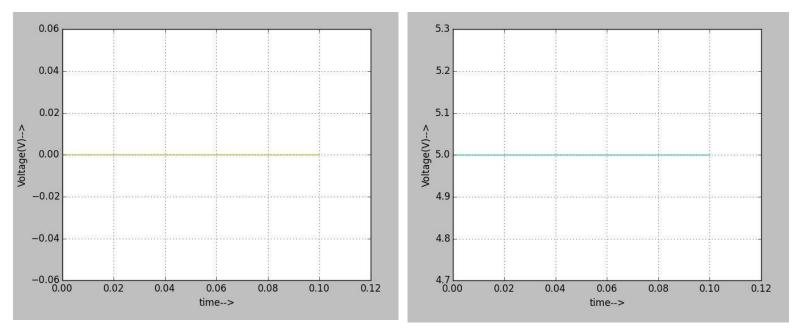

## OUTPUT when SEL(S)='0' EN='0'

SEL S (V9=0v)

EN( v10 = 0v)

Yb

# OUTPUT when SEL(S)='1' EN='0'

SEL S (V9=0v)

EN( v10 = 0v)

Yc

**REFERENCES:-**

1) <u>https://www.electronicshub.org/multiplexerandmultiplexing/</u>